#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

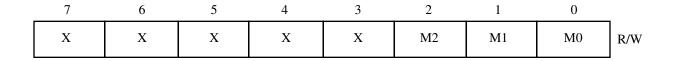

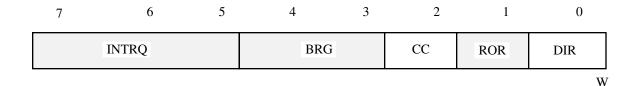

Sell For Cash Get Credit Receive a Trade-In Deal

## **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

GPIB-RS232

# GPIB-1014D User Manual

March 1997 Edition

**Part Number 320140-01**

### **National Instruments Corporate Headquarters**

6504 Bridge Point Parkway Austin, TX 78730-5039 (512) 794-0100

Technical support phone: (512) 795-8248 Technical support fax: (512) 794-5678

### **Branch Offices:**

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 90 527 2321, France 1 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Israel 03 5734815, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico5 520 2635, Netherlands 0348 433466, Norway 32 84 84 00, Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 20 51 51, Taiwan 02 377 1200, U.K. 01635 523545

### **Limited Warranty**

The GPIB-1014D is warranted against defects in materials and workmanship for a period of two years from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

### **Trademarks**

Product and company names listed are trademarks or trade names of their respective companies.

# Warning Regarding Medical and Clinical Use of National Instruments Products

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

# **Contents**

| Chapter 1                                                                      |            |

|--------------------------------------------------------------------------------|------------|

| Introduction                                                                   | 1_1        |

| What Your Kit Should Contain                                                   | 1_3        |

| Optional Equipment                                                             |            |

| Unpacking                                                                      | 1-3        |

| Chpacking                                                                      |            |

| Chapter 2                                                                      |            |

| General Description                                                            | 2-1        |

| Electrical Characteristics.                                                    | 2-1<br>7_1 |

| VMEbus Characteristics                                                         |            |

| VMEbus Slave-Addressing                                                        |            |

| VMEbus Slave-AddressingVMEbus Slave-Data                                       | 2-2<br>2-3 |

| VMEbus Master-Direct Memory Access                                             |            |

| Interrupter                                                                    |            |

| Data Transfer Bus (DTB) Requester                                              | 2-1<br>2.7 |

| VMEbus Modules Not Provided                                                    | 2 9        |

| Diagnostic Aids                                                                |            |

|                                                                                |            |

| Data Transfer Features                                                         |            |

| DMA Transfers from VMEbus Memory to the GPIB                                   | 2-9        |

| DMA Transfers from the GPIB to VMEbus Memory                                   | 2-9        |

| Programmed I/O Transfers                                                       |            |

| GPIB-1014D Functional Description                                              | 2-9        |

| Chapter 3                                                                      |            |

| •                                                                              | 2.1        |

| Configuration and Installation                                                 | 3-1        |

| Configuration                                                                  |            |

| Access Mode                                                                    |            |

| Base Address                                                                   |            |

| DMA Address Modifier Code Output                                               | 3-4        |

| Select Extended (32-Bit) Addressing Select Interrupt Source for DMAC Channel 2 | 3-6        |

| Select Interrupt Source for DMAC Channel 2                                     | 3-6        |

| VMEbus SYSFAIL* Driver Enable                                                  |            |

| Board Reset Source                                                             |            |

| Other Configuration Parameters                                                 |            |

| Installation                                                                   |            |

| Verification of System Compatibility                                           | 3-9        |

| Cabling                                                                        | 3-1        |

| Verification Testing                                                           | 3-12       |

| Clares Arms A                                                                  |            |

| Chapter 4                                                                      |            |

| Register Bit Descriptions                                                      | 4-1        |

| Register Maps                                                                  | 4-1        |

| Register Sizes                                                                 | 4-5        |

| Register Description                                                           | 4-5        |

| Register Description Format                                                    |            |

| Interface Registers                                                            | 4-7        |

| Data In Register (DIR)                                                         | 4-10       |

| Command/Data Out Register (CDOR)                                               | 4-1        |

| Interrupt Status Register I (ISRI)                  |            |     |

|-----------------------------------------------------|------------|-----|

| Interrupt Mask Register 1 (IMR1)                    |            |     |

| Interrupt Status Register 2 (ISR2)                  | 4-1        | 8   |

| Interrupt Mask Register 2 (IMR2)                    | 4-1        | 8   |

| Serial Poll Status Register (SPSR)                  | 4-2        | 1   |

| Serial Poll Mode Register (SPMR)                    | 4-2        | 1   |

| Address Status Register (ADSR)                      | 4-2        | 2   |

| Address Mode Register (ADMR)                        |            |     |

| Command Pass Through Register (CPTR)                | 4-2        | 2   |

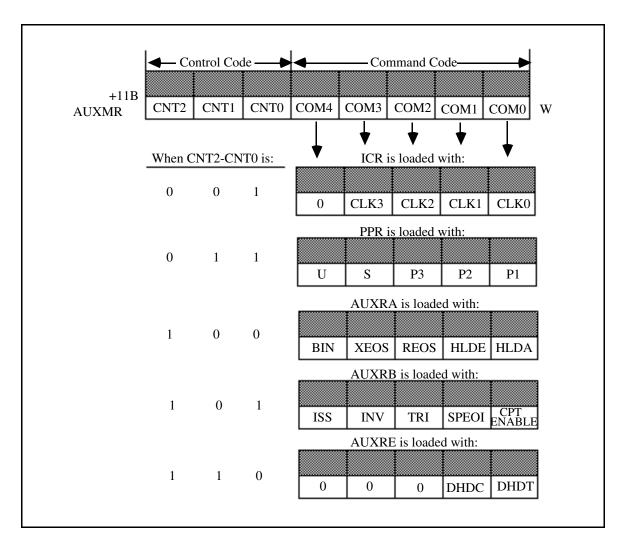

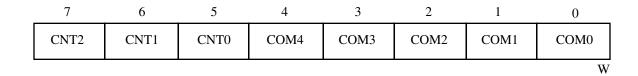

| Auxiliary Mode Register (AUXMR)                     | 4-3        | (   |

| Hidden Registers                                    | 4 - 3      | ,   |

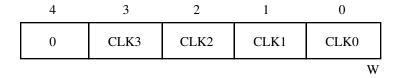

| Internal Counter Register (ICR)                     | 4-3        | ; 8 |

| Parallel Poll Register (PPR)                        | 4-3        | ,(  |

| Auxiliary Register A (AUXRA)                        | 4-4        |     |

| Auxiliary Register B (AUXRB)                        | <br>4_4    |     |

| Auxiliary Register E (AUXRE)                        | <br>4_4    | 4   |

| Address Register 0 (ADR0)                           |            |     |

| Address Register (ADR)                              | т-т<br>1_1 | 1   |

| Address Register (ADR)  Address Register 1 (ADR1)   | 4-4<br>1 1 | 9   |

| End Of String Pagister (EOSD)                       | 4-4        |     |

| End Of String Register (EOSR)                       | 4-5        |     |

| DMA Registers                                       | 4-J        | ,   |

| Address Registers                                   | 4-5        |     |

| Transfer Count Registers                            |            |     |

| Function Code Registers                             | 4-5        |     |

| Device Control Register (DCR)                       | 4-5        | (   |

| Operation Control Register (OCR)                    | 4-5        | 1   |

| Sequence Control Register (SCR)                     | 4-6        | )(  |

| Channel Control Register (CCR)                      | 4-6        | ) . |

| Channel Status Register (CSR)                       | 4-6        | )   |

| Channel Error Register (CER)                        |            |     |

| Channel Priority Register (CPR)                     | 4-6        | )(  |

| Interrupt Vector Registers                          | 4-6        | ĺ   |

| General Control Register (GCR)                      | 4-6        | , 8 |

| Configuration and Status Registers                  | 4-6        | ,(  |

| Configuration Register 1 (CFG1A and CFG1B)          | 4-6        | ,(  |

| Configuration Register 2 (CFG2A and CFG2B)          | 4-7        | 4   |

| Page Register (PGREG)                               | 4-7        | 2   |

| GPIB Status Register (GSRA and GSRB)                | 4-7        | 14  |

|                                                     |            |     |

| Chapter 5                                           |            |     |

| Programming Considerations                          | 5 1        |     |

| Initialization                                      | J-1<br>5 1 |     |

| The GPIB-1014D as GPIB Controller                   | J-1<br>5 2 | ,   |

| Deceming Controller In Charge and Active Controller | 5-3        | ,   |

| Becoming Controller-In-Charge and Active Controller | 5-3        |     |

| Sending Remote Multiline Messages (Commands)        | 5-4        |     |

| Going from Active to Standby Controller             | 5-4        |     |

| Going from Standby to Active Controller             | 5-5        | 1   |

| Going from Active to Idle Controller                | 2-6        | 1   |

| The GPIB-1014D as GPIB Talker and Listener          |            |     |

| Programmed Implementation of Talker and Listener    | 5-6        | )   |

| Addressed Implementation of the Talker and Listener |            |     |

| Address Mode 1                                      |            |     |

| Address Mode 2                                      | 5-7        |     |

|      | Address Mode 3                                       |               |          |

|------|------------------------------------------------------|---------------|----------|

|      | Sending/Receiving Messages                           | .5-8          | 3        |

|      | Using Direct Memory Access                           | .5-8          | 3        |

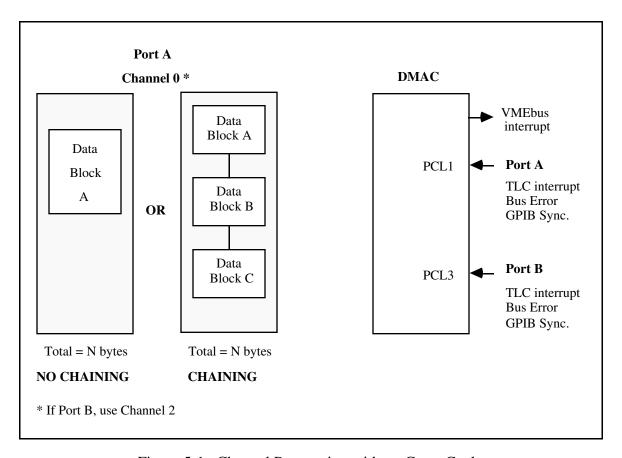

|      | DMA Transfers without Carry Cycle                    | .5-1          | 10       |

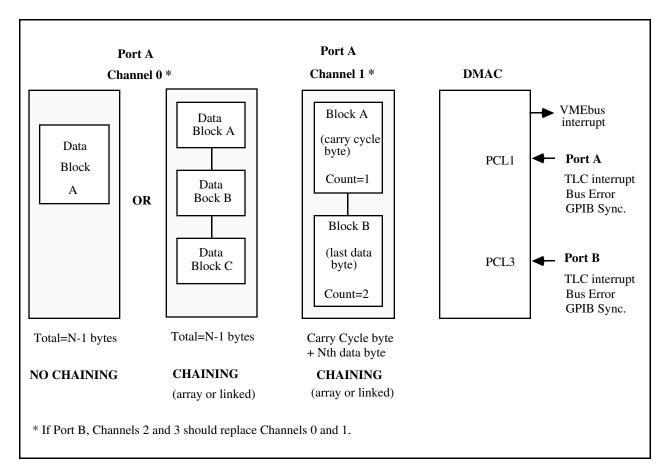

|      | DMA Transfers with Carry Cycle                       | .5-           | 13       |

|      | Polling During DMAs                                  | 5-            | 17       |

|      | Sending END or EOS                                   | 5-            | 17       |

|      | Checking Transfer Results and Handling Interrupts    |               |          |

|      | Terminating on END or EOS                            | 5-            | 19       |

|      | Using Programmed I/O                                 | .5-1<br>5-1   | 2C       |

|      | Sending and Receiving Data                           | ,5-2<br>5 '   | 20       |

|      | Schuling and Receiving Data                          | .J-2<br>5 1   | 20<br>20 |

|      | Sending END or EOS                                   | .J-2          | 20<br>20 |

|      | Terminating on END or EOS                            | .J-2          | 20<br>20 |

|      | Interrupts                                           | .3-4          | 2U<br>20 |

|      | Serial Polls                                         |               |          |

|      | Conducting Serial Polls                              | .5-2          | 22       |

|      | Responding to a Serial Poll                          | .5-2          | 22       |

|      | Parallel Polls                                       | .5-2          | 23       |

|      | Conducting a Parallel Poll                           | .5-2          | 23       |

|      | Responding to a Parallel Poll                        | .5-2          | 24       |

|      | Software Porting                                     | .5-2          | 25       |

|      | Porting GPIB-1014 Software to GPIB-1014D             | .5-2          | 25       |

| Theo | ry of Operation                                      | . <b>6-</b> 1 | 1        |

|      | Data Lines                                           |               |          |

|      | Slave Read and Write Transfers                       |               |          |

|      | DMA Transfers                                        |               |          |

|      | Control Signals                                      | .6-2          | 2        |

|      | Address                                              |               |          |

|      | Address Decoder                                      |               |          |

|      | Clock and Reset Circuitry                            |               |          |

|      | Configuration Registers                              | .6-4          | 4        |

|      | Configuration Register 1 (CFG1A or CFG1B)            | .6-:          | 5        |

|      | Configuration Register 2 (CFG2A or CFG2B)            | .6-5          | 5        |

|      | GPIB Status Register (GSRA or GSRB)                  | .6-6          | 5        |

|      | Page Register (PGREG)                                | .6-6          | 6        |

|      | Timing State Machine Circuitry                       | .6-6          | 5        |

|      | Slave Cycles                                         |               |          |

|      | DMA Cycles                                           |               |          |

|      | DMA Gating and Control Circuitry                     | .6-8          | 3        |

|      | Interrupter Circuitry                                | .6-0          | 9        |

|      | Interrupter Circuitry                                | 6-            | 10       |

|      | GPIB Synchronization and Interrupt Control Circuitry | 6-            | 11       |

|      | TLC Interrupt                                        | 6-            | 11       |

|      | GPIB Synchronization Interrupt                       |               |          |

|      | Bus Error Interrupt                                  | 6-            | 12       |

|      | DMA Controller                                       |               |          |

|      | DMAC Channel Operation                               |               |          |

|      | Initialization and Transfer Phases                   |               |          |

|      | Device (TLC)/DMAC Communication                      |               |          |

|      | Data Transfers                                       |               |          |

|      | Data 11ansiers                                       | . 0-          | , I      |

| Operands and Addressing                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-14                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Address Register Operation                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| Transfer Count Register Operation                                                                                                                                                                                                                                                                                                                                                                                                              | 6-15                                          |

| Initiation and Control of Channel Operation                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

| Initiating the Operation                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |

| The Continue Mode of Operation                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| Halt                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

| Software Abort                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

| Block Termination                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |

| Continued Operations.                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |

| Multiple Block Operations                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

| Linked Chaining Operations                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| Error Conditions                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

| Configuration Error.                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

| Operation Timing Error                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               |

| Address Error                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |

| Bus Error                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

| Count Error                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |

| Abort                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |

| GPIB Interfaces (NEC μPD7210s)                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| Test and Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-22                                          |

| DMA Stand Alone Testing                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-22                                          |

| GPIB Interface Testing                                                                                                                                                                                                                                                                                                                                                                                                                         | 6-22                                          |

| Chapter 7 Diagnostic and Troubleshooting Test Procedures Interpreting Test Procedures                                                                                                                                                                                                                                                                                                                                                          | 7-1<br>7-1                                    |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-1                                           |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures  GPIB-1014D Hardware Installation Tests                                                                                                                                                                                                                                                                                                                           | 7-1                                           |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures  GPIB-1014D Hardware Installation Tests  Appendix A                                                                                                                                                                                                                                                                                                               | 7-1<br>7-2                                    |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures  GPIB-1014D Hardware Installation Tests  Appendix A                                                                                                                                                                                                                                                                                                               | 7-1<br>7-2                                    |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures  GPIB-1014D Hardware Installation Tests  Appendix A  Specifications                                                                                                                                                                                                                                                                                               | 7-1<br>7-2                                    |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B                                                                                                                                                                                                                                                                                     | 7-1<br>7-2<br>A-1                             |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams                                                                                                                                                                                                                                    | 7-1<br>7-2<br>A-1                             |

| Diagnostic and Troubleshooting Test Procedures Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C                                                                                                                                                                                                                         | A-1B-1                                        |

| Diagnostic and Troubleshooting Test Procedures Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C Sample Programs                                                                                                                                                                                                         | A-1B-1                                        |

| Diagnostic and Troubleshooting Test Procedures                                                                                                                                                                                                                                                                                                                                                                                                 | A-1B-1                                        |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C Sample Programs  Appendix D Multiline Interface Messages                                                                                                                                                               | A-1B-1                                        |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C Sample Programs  Appendix D Multiline Interface Messages  Appendix E                                                                                                                                                   | A-1B-1D-1                                     |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C Sample Programs  Appendix D Multiline Interface Messages  Appendix E                                                                                                                                                   | A-1B-1D-1                                     |

| Diagnostic and Troubleshooting Test Procedures Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C Sample Programs  Appendix D Multiline Interface Messages  Appendix E Operation of the GPIB                                                                                                                              | A-1B-1D-1                                     |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C Sample Programs  Appendix D Multiline Interface Messages  Appendix E Operation of the GPIB Types of Messages Talkers, Listeners, and Controllers                                                                       |                                               |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C Sample Programs  Appendix D Multiline Interface Messages  Appendix E Operation of the GPIB Types of Messages Talkers, Listeners, and Controllers                                                                       |                                               |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C Sample Programs  Appendix D Multiline Interface Messages  Appendix E Operation of the GPIB Types of Messages Talkers, Listeners, and Controllers The Controller-In-Charge and System Controller                        |                                               |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C Sample Programs  Appendix D Multiline Interface Messages  Appendix E Operation of the GPIB Types of Messages Talkers, Listeners, and Controllers The Controller-In-Charge and System Controller GPIB Signals and Lines |                                               |

| Diagnostic and Troubleshooting Test Procedures  Interpreting Test Procedures GPIB-1014D Hardware Installation Tests  Appendix A Specifications  Appendix B PAL Drawings, Parts List, and Schematic Diagrams  Appendix C Sample Programs  Appendix D Multiline Interface Messages  Appendix E Operation of the GPIB Types of Messages Talkers, Listeners, and Controllers The Controller-In-Charge and System Controller                        | 7-17-2A-1B-1B-1D-1E-1E-1E-1E-2E-2E-2E-2E-2E-2 |

|             | NDAC (not data accepted)                            |         |

|-------------|-----------------------------------------------------|---------|

|             | DAV (data valid)                                    |         |

|             | Interface Management Lines                          |         |

|             | IFC (interface clear)                               |         |

|             | REN (remote enable)                                 |         |

|             | SRQ (service request)                               |         |

|             | EOI (end or identify)                               |         |

| Phys        | sical and Electrical Characteristics                |         |

|             | figuration Requirements                             |         |

| Rela        | ted Document                                        | E-7     |

| Appendix    | : <b>F</b>                                          |         |

| Mnemoni     | cs Key                                              | F-1     |

| Appendix    |                                                     |         |

| Customer    | · Communication                                     | G-1     |

| Index       |                                                     | Index-1 |

|             |                                                     |         |

|             | Figures                                             |         |

| Figure 1-1. | GPIB-1014D Interface Board                          | 1-2     |

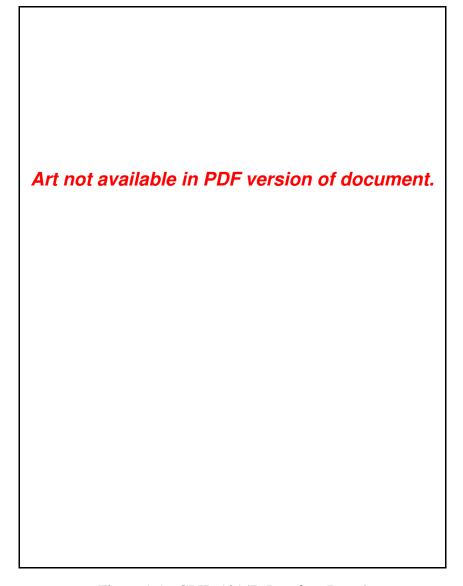

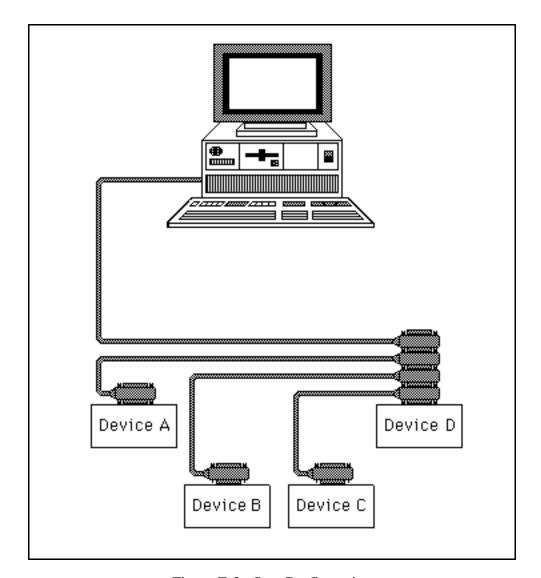

| Figure 2-1. | GPIB-1014D with a VMEbus Computer                   | 2-10    |

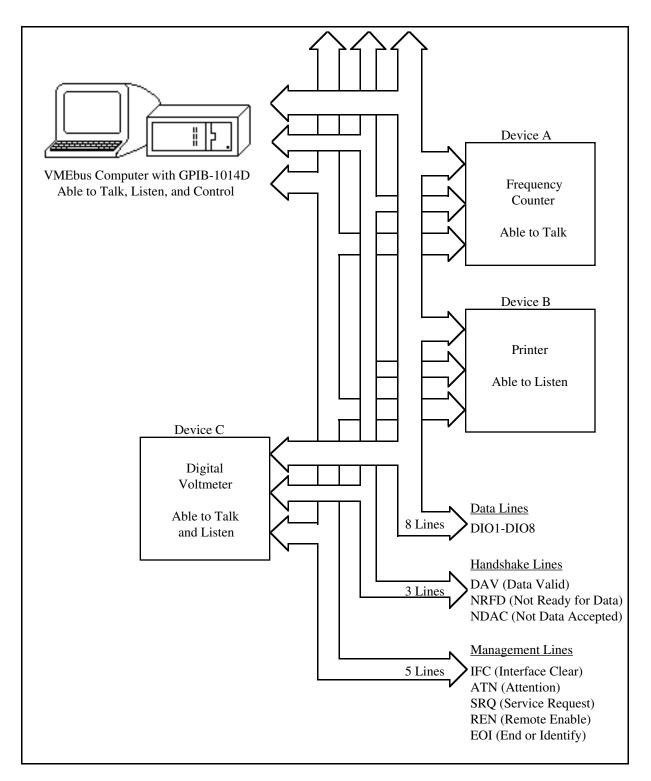

| Figure 2-2. | GPIB-1014D in a Multiprocessor Application          | 2-11    |

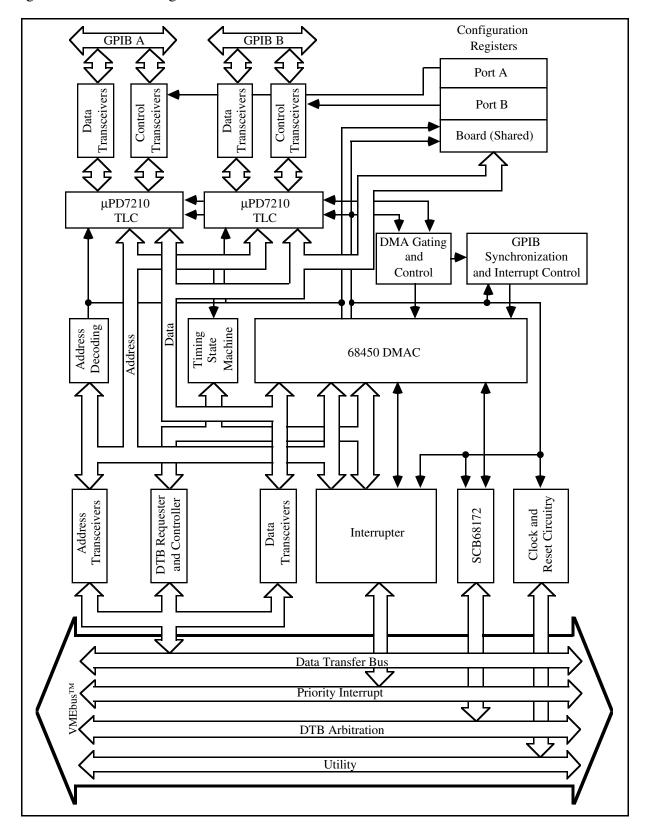

| Figure 2-3. | GPIB-1014D Block Diagram                            | 2-12    |

| F: 2 1      | CDID 1014D Dente I access Diagrams                  | 2.2     |

| Figure 3-1. | GPIB-1014D Parts Locator Diagram                    | 3-2     |

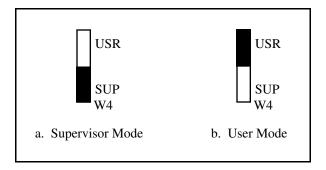

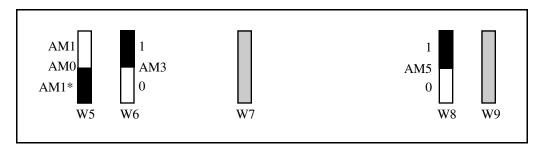

|             | Access Mode After RESET                             |         |

|             | Default Settings of AM Code Switches W5, W6, and W8 |         |

|             | 32-bit Addressing Switch                            |         |

|             | DMAC PCL2* Signal Selection                         |         |

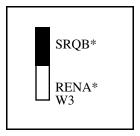

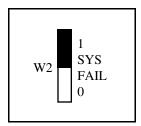

|             | VMEbus SYSFAIL* Driver Enabled                      |         |

|             | Board Reset Source                                  |         |

| C           |                                                     |         |

| Figure 4-1. | GPIB-1014D Registers Address Space                  | 4-1     |

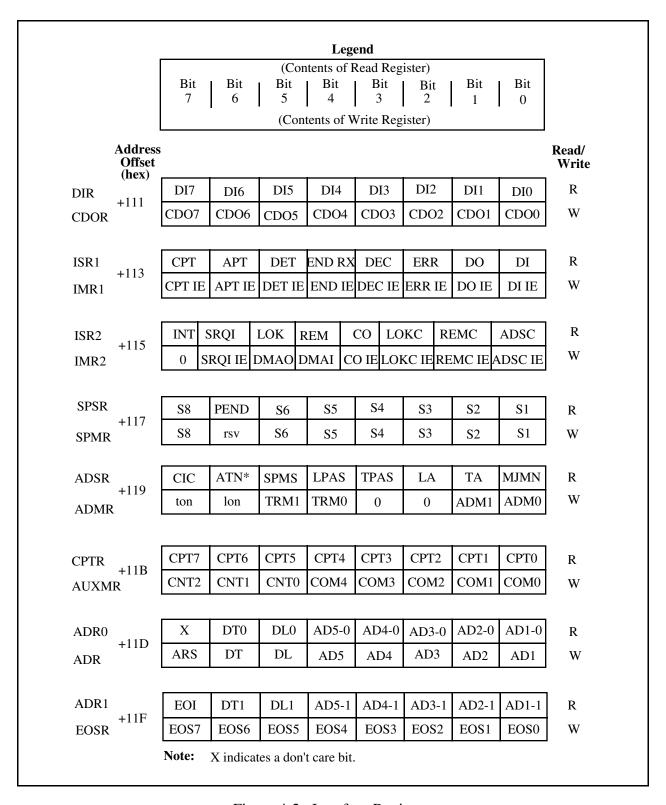

| Figure 4-2. | Interface Registers                                 | 4-8     |

|             | Writing to the Hidden Registers                     |         |

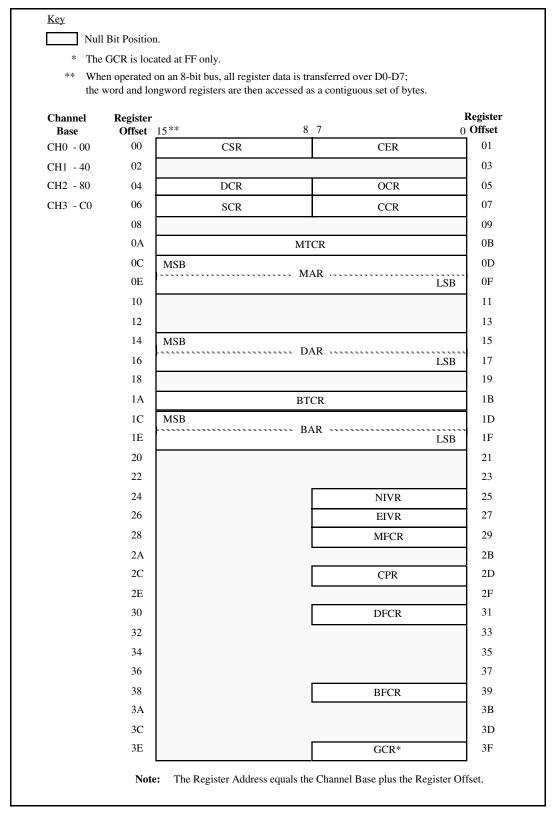

| Figure 4-4. | DMA Register Memory Map                             | 4-52    |

| Figure 5-1. | Channel Preparation without Carry Cycle             | 5-10    |

| Figure 5-2. | DMA Transfer with Carry Cycle                       | 5-13    |

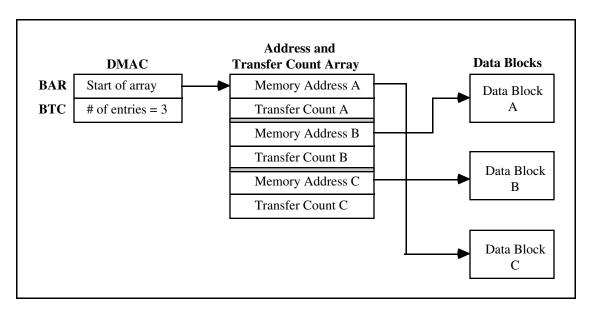

|             | Array Format for Array Chaining Modes               |         |

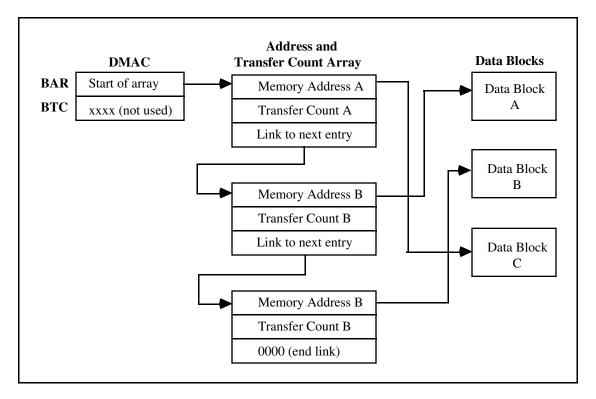

| Figure 6-2. | Array Format for Linked Chaining Modes              | 6-19    |

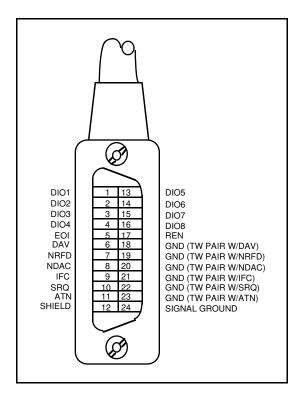

| Figure E-1. | GPIB Connector and the Signal Assignment            | E-4     |

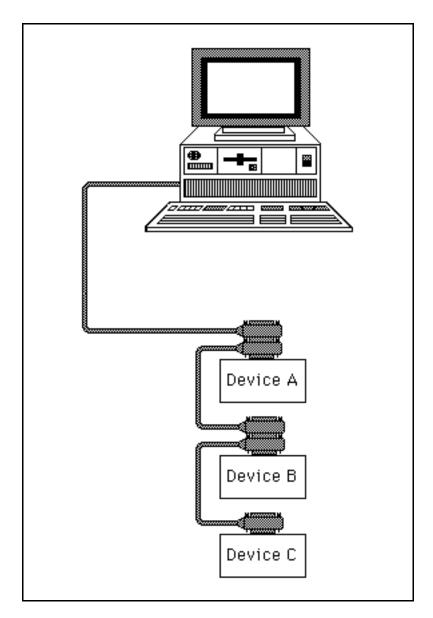

|             | Linear Configuration                                |         |

|             | Star Configuration                                  |         |

## **Tables**

| Table | 2-1. | GPIB-1014D Signals                                                  | 2-1  |

|-------|------|---------------------------------------------------------------------|------|

| Table | 2-2. | μPD7210 Internal GPIB Interface Registers (Port A and Port B)       | 2-4  |

|       |      | 68450 Internal DMA Registers                                        |      |

| Table | 2-4. | Configuration, Page, and GPIB Status Registers of Port A and Port B | 2-6  |

| Table | 2-5. | GPIB-1014D IEEE-488 Interface Capabilities                          | 2-14 |

| Table | 2-6. | GPIB-1014D IEEE-1014 Compliance Levels                              | 2-16 |

| Table | 3-1. | Programming Values for Default Settings of Jumpers W5, W6, and W8   | 3-4  |

|       |      | Setting the Address Modifier Code bits (AM5-AM0)                    |      |

|       |      | GPIB-1014D Pin Assignment on VMEbus Connector P1                    |      |

|       |      | GPIB-1014D Pin Assignment on VMEbus Connector P2                    |      |

| Table | 4-1. | GPIB-1014D Port A Register Map                                      | 4-2  |

|       |      | GPIB-1014D Port B Register Map                                      |      |

| Table | 4-3. | Clues to Understanding Mnemonics                                    | 4-6  |

|       |      | Multiline GPIB Commands Recognized by the μPD7210                   |      |

| Table | 4-5. | Auxiliary Command Summary                                           | 4-31 |

| Table | 4-6. | Auxiliary Commands: Detail Description                              | 4-32 |

| Table | 4-7. | Examples of Configuring the Parallel Poll Register                  | 4-40 |

| Table | 4-8. | DMAC DMA Channel Register Set                                       | 4-51 |

|       |      |                                                                     |      |

# **Preface**

The GPIB-1014D is a double-height circuit board that interfaces the VMEbus to the IEEE-488 General Purpose Interface Bus (GPIB). The GPIB-1014D is used to implement VMEbus test and measurement systems using standard interconnecting cables.

# **Organization of This Manual**

This manual describes the mechanical and electrical aspects of the GPIB-1014D and contains information concerning its operation and programming. The manual is divided into the following chapters and appendixes:

- Chapter 1, *Introduction*, describes the GPIB-1014D features, lists the contents of your GPIB-1014D kit, and explains how to unpack the GPIB-1014D kit.

- Chapter 2, *General Description*, contains the physical and electrical specifications for the GPIB-1014D and describes the characteristics of key interface board components.

- Chapter 3, *Configuration and Installation*, describes the steps needed to configure the GPIB-1014D hardware and to verify that it is functioning properly.

- Chapter 4, *Register Bit Descriptions*, contains detailed GPIB Interface register descriptions of the NEC μPD7210 GPIB Talker/Listener/Controller, the internal DMA registers of the 68450 DMA Controller, and Configuration Registers of the GPIB-1014D as well as summary tables for easy reference.

- Chapter 5, *Programming Considerations*, explains important considerations for programming the GPIB-1014D.

- Chapter 6, *Theory of Operation*, contains a functional overview of the GPIB-1014D board and explains the operation of each functional block making up the GPIB-1014D.

- Chapter 7, *Diagnostic and Troubleshooting Test Procedures*, contains test procedures for determining if the GPIB-1014D is installed and operating correctly.

- Appendix A, *Specifications*, lists the specifications of the GPIB-1014D.

- Appendix B, *PAL Drawings*, *Parts List*, *and Schematic Diagrams*, contains the PAL drawings, a parts list, and detailed schematic diagrams of the GPIB-1014D.

- Appendix C, *Sample Programs*, contains sample programs in 68000 Assembly Language code for implementing the most commonly used GPIB functions. Line-by-line comments provide an explanation of each function.

- Appendix D, *Multiline Interface Messages*, contains a listing of the multiline GPIB interface messages.

- Appendix E, Operation of the GPIB, describes the operation of the GPIB.

- Appendix F, *Mnemonics Key*, contains an alphabetical listing of all mnemonics used in this manual and indicates whether the mnemonic represents a bit, register, function, remote message, local message or a state.

- Appendix G, *Customer Communication*, contains forms you can use to request help from National Instruments or to comment on our products and manuals.

- The *Index* contains an alphabetical list of key terms and topics in this manual, including the page where you can find each one.

## **Conventions Used in This Manual**

italic Italic text denotes emphasis, a cross reference, or an introduction to a key concept.

### **Abbreviations**

The following are the metric system prefixes for use with abbreviations for units of measure:

| Prefix      | Meaning                | Value                                                                       |

|-------------|------------------------|-----------------------------------------------------------------------------|

| n<br>μ<br>m | nano<br>micro<br>milli | 10 <sup>-9</sup><br>10 <sup>-6</sup><br>10 <sup>-3</sup><br>10 <sup>3</sup> |

| k<br>M      | kilo<br>mega           | $\frac{10^3}{10^6}$                                                         |

The following are the accepted abbreviations for units of measure used in the text of this manual.

| A      | ampere                 |

|--------|------------------------|

| C      | Celcius                |

| 0      | degree                 |

| hex    | hexadecimal            |

| Hz     | hertz                  |

| in.    | inch                   |

| K      | kilobyte (1,024 bytes) |

| kbytes | 1,000 bytes            |

| m      | meter                  |

| %      | percent                |

| sec    | second                 |

| V      | volt                   |

|        |                        |

### Acronyms

**VDC**

volts direct current

### **Related Documents**

The following manuals contain information that you may find helpful as you read this manual:

- ANSI/IEEE Std. 488-1978, IEEE Standard Digital Interface for Programmable Instrumentation.

- ANSI/IEEE Std. 1014-1987, IEEE Standard for a Versatile Backplane Bus: VMEbus.

- μPD7210 GPIB-IFC User Manual, NEC Electronics U.S.A., Inc..

- μPD7210 Intelligent GPIB Interface Controller Engineering Data Sheet, NEC Electronics U.S.A., Inc., Microcomputer Division.

- How to Interface a Microcomputer System to a GPIB, (& The NEC μPD7210 TLC), NEC Electronics U.S.A., Inc.

- Motorola Semiconductor Technical Data MC68450 Advance Information Direct Memory Access Controller (DMAC), Motorola, Inc.

- Hitachi Microcomputer System HD68450 DMAC (Direct Memory Access Controller).

# **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix G, *Customer Communication*, at the end of this manual.

# Chapter 1 Introduction

The GPIB-1014D is a high-performance IEEE-488 interface for the VMEbus. By using the GPIB-1014D, a VMEbus-based computer is able to control IEEE-488 compatible engineering, scientific, or medical instruments. The GPIB-1014D has the following features:

- Two independent IEEE-488 interfaces

- Complete IEEE-488 Talker/Listener/Controller (TLC) capability for each IEEE-488 interface using two NEC μPD7210 GPIB TLC chips

- Ability to monitor the status of all GPIB control lines for each interface (necessary for IEEE-488.2 compliance)

- DMA transfers

- Data rates up to 500 kbytes/sec

- Unlimited data block lengths

- Full 32-bit addressing

- Automatic carry cycle operation

- GPIB synchronization detection

- Release On Request capability

- General purpose DMA capability

- Complete software control through programmable configuration parameters

- One out of four Bus Request/Grant lines

- One out of seven Interrupt Request lines

- Supervisor or User access

- Red/Green SYSFAIL LED indicator

- Local Master Reset

- IEEE-1014 (VMEbus) standard compliance

- Complete software compatibility with the GPIB-1014

The GPIB-1014D conforms to all requirements and conventions specified in the ANSI/IEEE Std. 1014-1987. Hereafter, the General Purpose Interface Bus is referred to as the GPIB, the GPIB standard is referred to as the IEEE-488 standard, and the ANSI/IEEE Std. 1014-1987 is referred to as the IEEE-1014 standard.

Introduction Chapter 1

Figure 1-1. GPIB-1014D Interface Board

The GPIB-1014D interface kit includes hardware and programming examples to implement the GPIB functions. Optional cables are supplied for interconnection with other devices on the GPIB.

Chapter 1 Introduction

# What Your Kit Should Contain

Your GPIB-1014D kit contains one of the following boards:

- GPIB-1014D-1

- GPIB-1014D-1S

The GPIB-1014D-1S board contains no front panel.

# **Optional Equipment**

You can contact National Instruments to order the following optional equipment:

- Single-shielded Type X1 GPIB cables (1 m, 2 m, or 4 m)

- Double-shielded Type X2 GPIB cables (1 m, 2 m, or 4 m)

- GPIB Monitor/Analyzer

- GPIB-400

- GPIB-410

# Unpacking

Follow these steps when unpacking your GPIB-1014D.

- 1. Your GPIB-1014D board is shipped packaged in an antistatic plastic bag to prevent electrostatic damage to the board. Several components on the board can be damaged by electrostatic discharge. To avoid such damage in handling the board, touch the plastic bag to a metal part of your VMEbus computer chassis before removing the board from the bag.

- 2. Remove the board from the bag and inspect the board for loose components or any other sign of damage. Notify National Instruments if the board appears damaged in any way. *Do not* install a damaged board into your computer.

This chapter contains the physical and electrical specifications for the GPIB-1014D and describes the characteristics of key interface board components.

### **Electrical Characteristics**

All integrated circuit drivers and receivers used on the GPIB-1014D meet the requirements of the VMEbus Specification and the IEEE-1014 standard. Table 2-1 contains a list of the VMEbus signals used by the GPIB-1014D and the electrical loading presented by the circuitry on the interface board (in terms of device types and their part numbers).

**Note:** The asterisk (\*) after the bus signal indicates that the signal is active low.

Table 2-1. GPIB-1014D Signals

| Bus Signals        | Driver Device<br>Part Number | Receiver Device<br>Part Number |

|--------------------|------------------------------|--------------------------------|

| D00-D15            | F245                         | F245                           |

| A15-A10            | AS573                        | -                              |

| A9                 | AS573                        | F125                           |

| A8                 | AS573                        | AS373                          |

| A07-A01            | F245                         | F245                           |

| AM5-AM3, AM0       | F244                         | LS2521                         |

| AM2                | F244                         | F32                            |

| DS0*, DS1*, WRITE* | F1243                        | F1243                          |

| AS*                | 68172 (BUSCON)               | 68172 (BUSCON)                 |

| LWORD*             | F244                         | LS2521                         |

| IACK*              | F244                         | LS240                          |

| SYSCLK             | -                            | LS241                          |

| BG0IN*-BG3IN*      | -                            | LS241                          |

| BG0OUT*-BG3OUT*    | F04                          | -                              |

(continues)

Table 2-1. GPIB-1014D Signals (continued)

| Bus Signals | Driver Device<br>Part Number | Receiver Device<br>Part Number |

|-------------|------------------------------|--------------------------------|

| DTACK*      | F38                          | F125                           |

| BR0*-BR3*   | F38                          | PAL22PIO                       |

| BBSY*       | 68172 (BUSCON)               | 68172 (BUSCON)                 |

| IACKIN*     | -                            | LS241                          |

| IACKOUT*    | F32                          | -                              |

| IRQ1*-IRQ7* | 74145                        | _                              |

| BERR*       | F38                          | F125                           |

| SYSFAIL*    | F38                          | -                              |

| SYSRESET*   | _                            | LS241                          |

All GPIB transceivers meet the requirements of the IEEE-488 standard. The components used are as follows:

/S:

**Component Designation**

Data Transceivers DS75160AN

Control Transceivers DS75162AN

**Note:** The GPIB-1014D requires regulated +5 VDC power from the VMEbus. Current load is typically 2.5 A (2.9 A maximum).

# **VMEbus Characteristics**

**Transceivers**

The following paragraphs describe each of the VMEbus modules on the GPIB-1014D: slave, master, interrupter, and requester. Table 2-5 at the end of this chapter summarizes the capabilities of these modules.

# VMEbus Slave-Addressing

The GPIB-1014D occupies 1,024 bytes (512 words) in the A16 (short) I/O space. As a VMEbus slave, it only responds when the address modifier (AM) lines specify a short supervisory access (AM code = 2D) or short nonpriviledged access (AM code = 29). The board responds to short 16-bit addresses.

The GPIB-1014D is divided into two ports: Port A and Port B. Each port has an identical set of registers. The GPIB-1014D first compares address lines A15 through A10 with its base address to generate its board select signal. It then decodes address line A9 in determining to which port it will talk and decodes the lowest eight address lines A8 through A1 to address the following components and registers.

- The 68450 DMA Controller (DMAC)

- The µPD7210 GPIB Talker/Listener/Controllers (TLC) (one for each port)

- Two 8-bit, write-only Configuration Registers (two for each port)

- One GPIB Status Register (one for each port)

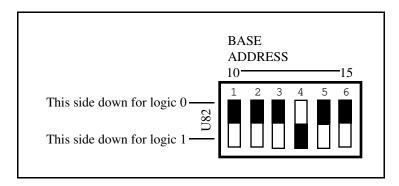

- One Page Register

The base address of the board is configured through the switch set U82 on the interface board. See Chapter 3, *Configuration and Installation*, for instructions on how to set the base address of the board.

### **VMEbus Slave-Data**

The GPIB-1014D can function as a VMEbus slave, decoding short I/O addresses and commands from a VMEbus master. The  $\mu$ PD7210 TLCs, the Configuration Registers, the GPIB Status Registers, and the Page Register function as 8-bit slaves, allowing data to be transferred to and from the VMEbus master on data lines D07 through D00. The 68450 can function as an 8- or 16-bit slave, allowing 8- or 16-bit transfers on data lines D15 through D00. The board is designed to accommodate Address Only (ADO) cycles. In VMEbus terminology, the slave module of the board is designated as SADO16 / D16 and D08(EO).

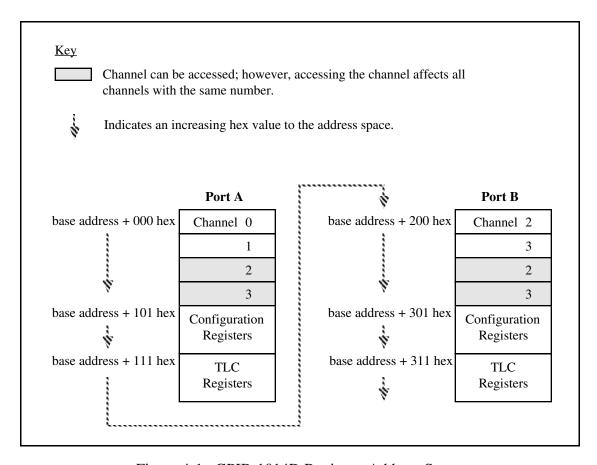

Ports A and B of the GPIB-1014D have an identical set of registers that consist of the GPIB Interface Registers, two Configuration Registers, and one GPIB Status Register. The Page Register, along with some bits of the Configuration Registers, are shared by both ports, but can be written in the address space of either port. The ports were designed so that the base address of Port A is at the base address of the board, and the base address of Port B is at the base address of the board + 200 (hex). Thus, if the Data In Register (DIR) of Port A is located at base address + 111 (hex), then the DIR of Port B is located at base address + 311 (hex).

The GPIB Interface Registers associated with the  $\mu$ PD7210s are addressed relative to the base address of the GPIB-1014D as shown in Table 2-2. The DMA registers internal to the 68450 are shown in Table 2-3. The Configuration Registers, the GPIB Status Registers, and the Page Register of the GPIB-1014D are shown in Table 2-4.

Table 2-2. μPD7210 Internal GPIB Interface Registers (Port A and Port B)

|     | lress<br>ex offset)<br>Port B | Mode         | Register                      |         | Size   |

|-----|-------------------------------|--------------|-------------------------------|---------|--------|

| 111 | 311                           | R            | Data In Register              | (DIR)   | 8 bits |

| 111 | 311                           | W            | Control/Data Out Register     | (CDOR)  | 8 bits |

| 113 | 313                           | R            | Interrupt Status Register 1   | (ISR1)  | 8 bits |

| 113 | 313                           | W            | Interrupt Mask Register 1     | (IMR1)  | 8 bits |

| 115 | 315                           | R            | Interrupt Status Register 2   | (ISR2)  | 8 bits |

| 115 | 315                           | W            | Interrupt Mask Register 2     | (IMR2)  | 8 bits |

| 117 | 317                           | R            | Serial Poll Status Register   | (SPSR)  | 8 bits |

| 117 | 317                           | W            | Serial Poll Mode Register     | (SPMR)  | 8 bits |

| 119 | 319                           | R            | Address Status Register       | (ADSR)  | 8 bits |

| 119 | 319                           | W            | Address Mode Register         | (ADMR)  | 8 bits |

| 11B | 31B                           | R            | Command Pass Through Register | (CPTR)  | 8 bits |

| 11B | 31B                           | $\mathbf{W}$ | Auxiliary Mode Register       | (AUXMR) | 8 bits |

| 11D | 31D                           | R            | Address Register 0            | (ADR0)  | 8 bits |

| 11D | 31D                           | W            | Address Register              | (ADR)   | 8 bits |

| 11F | 31F                           | R            | Address Register 1            | (ADR1)  | 8 bits |

| 11F | 31F                           | W            | End Of String Register        | (EOSR)  | 8 bits |

Table 2-3. 68450 Internal DMA Registers

| Address (Base<br>+ hex offset)                     | Mode                                                 | Register                                                                                                                                                                                                                                           |                                                                                                    | Channel                         | Size                                                                                   |

|----------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------|

| 0A<br>0C<br>29<br>14<br>31<br>1A<br>1C<br>39       | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W        | Memory Transfer Counter Register<br>Memory Address Register<br>Memory Function Code Register<br>Device Address Register<br>Device Function Code Register<br>Base Transfer Counter Register<br>Base Address Register<br>Base Function Code Register | (MTCR0)<br>(MAR0)<br>(MFCR0)<br>(DAR0)<br>(DFCR0)<br>(BTCR0)<br>(BAR0)<br>(BFCR0)                  | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 16 bits<br>32 bits<br>8 bits<br>32 bits<br>8 bits<br>16 bits<br>32 bits<br>8 bits      |

| 00<br>01<br>04<br>05<br>06<br>07<br>2D<br>25<br>27 | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W | Channel Status Register Channel Error Register Device Control Register Operation Control Register Sequence Control Register Channel Control Register Channel Priority Register Normal Interrupt Vector Register Error Interrupt Vector Register    | (CSR0)<br>(CER0)<br>(DCR0)<br>(OCR0)<br>(SCR0)<br>(CCR0)<br>(CCR0)<br>(CPR0)<br>(NIVR0)<br>(EIVR0) | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 8 bits<br>8 bits<br>8 bits<br>8 bits<br>8 bits<br>8 bits<br>8 bits<br>8 bits<br>8 bits |

(continues)

Table 2-3. 68450 Internal DMA Registers (continues)

| 54 R/W Device Address Register (DAR1) 1 32 bits 54 R/W Device Function Code Register (DFCR1) 1 8 bits 55 R/W Base Transfer Counter Register (BTCR1) 1 16 bits 55 R/W Base Address Register (BTCR1) 1 16 bits 55 R/W Base Address Register (BAR1) 1 32 bits 79 R/W Base Function Code Register (BFCR1) 1 8 bits 40 R/W Channel Status Register (CSR1) 1 8 bits 41 R Channel Error Register (CER1) 1 8 bits 44 R/W Device Control Register (DCR1) 1 8 bits 45 R/W Operation Control Register (OCR1) 1 8 bits 46 R/W Sequence Control Register (OCR1) 1 8 bits 46 R/W Sequence Control Register (CCR1) 1 8 bits 47 R/W Channel Priority Register (CCR1) 1 8 bits 60 R/W Channel Priority Register (CPR1) 1 8 bits 67 R/W Channel Priority Register (IVR1) 1 8 bits 67 R/W Error Interrupt Vector Register (MIVR1) 1 8 bits 67 R/W Error Interrupt Vector Register (MIVR1) 1 8 bits 67 R/W Device Address Register (MFCR2) 2 32 bits 94 R/W Memory Address Register (MFCR2) 2 32 bits 94 R/W Device Address Register (BAR2) 2 32 bits 94 R/W Device Address Register (BAR2) 2 32 bits 94 R/W Base Transfer Counter Register (BFCR2) 2 8 bits 95 R/W Base Address Register (BAR2) 2 32 bits 96 R/W Base Transfer Counter Register (BFCR2) 2 8 bits 97 R/W Base Transfer Counter Register (BRC2) 2 8 bits 98 R/W Base Transfer Counter Register (BRC2) 2 8 bits 98 R/W Base Transfer Counter Register (BRC2) 2 8 bits 99 R/W Base Function Code Register (BRC2) 2 8 bits 80 R/W Channel Status Register (CSR2) 2 8 bits 81 R Channel Error Register (DCR2) 2 8 bits 84 R/W Device Control Register (DCR2) 2 8 bits 85 R/W Operation Control Register (CCR2) 2 8 bits 86 R/W Sequence Control Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 86 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 86 R/W Channel Priority Register (CCR2) 2 8 bits 86 R/W Channel Priority Register (CCR2) 2 8 bits 86 R/W | Address (Base<br>+ hex offset) | Mode | Register                         | Channel | Size           |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|----------------------------------|---------|----------------|---------|

| 4C         R/W         Memory Address Register         (MAR1)         1         32 bits           69         R/W         Memory Function Code Register         (MFCR1)         1         32 bits           54         R/W         Device Address Register         (DAR1)         1         32 bits           71         R/W         Device Function Code Register         (DFCR1)         1         8 bits           5A         R/W         Base Transfer Counter Register         (BAR1)         1         32 bits           5A         R/W         Base Address Register         (BAR1)         1         32 bits           5A         R/W         Base Address Register         (BAR1)         1         32 bits           40         R/W         Base Address Register         (BRR1)         1         32 bits           40         R/W         Base Address Register         (CSR1)         1         8 bits           40         R/W         Channel Status Register         (CER1)         1         8 bits           41         R         Channel Error Register         (DCR1)         1         8 bits           45         R/W         Operation Control Register         (SCR1)         1         8 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4A                             | R/W  | Memory Transfer Counter Register | (MTCR1) | 1              | 16 bits |

| 69 R/W Device Address Register (MFCR1) 1 8 bits 71 R/W Device Function Code Register (DAR1) 1 32 bits 71 R/W Device Function Code Register (DFCR1) 1 8 bits 5A R/W Base Transfer Counter Register (BTCR1) 1 16 bit 5C R/W Base Address Register (BTCR1) 1 132 bits 79 R/W Base Function Code Register (BFCR1) 1 8 bits 40 R/W Channel Status Register (CER1) 1 8 bits 41 R Channel Error Register (CER1) 1 8 bits 44 R/W Device Control Register (DCR1) 1 8 bits 45 R/W Operation Control Register (OCR1) 1 8 bits 46 R/W Sequence Control Register (OCR1) 1 8 bits 46 R/W Sequence Control Register (CCR1) 1 8 bits 47 R/W Channel Control Register (CCR1) 1 8 bits 65 R/W Channel Priority Register (CCR1) 1 8 bits 66 R/W Sequence Control Register (CCR1) 1 8 bits 67 R/W Channel Priority Register (CCR1) 1 8 bits 67 R/W Error Interrupt Vector Register (MTCR2) 2 16 bits 80 R/W Memory Address Register (MTCR2) 2 32 bits 80 R/W Memory Function Code Register (MTCR2) 2 32 bits 81 R/W Device Address Register (DAR2) 2 32 bits 94 R/W Device Address Register (DAR2) 2 32 bits 94 R/W Device Address Register (BAR2) 2 32 bits 94 R/W Device Address Register (BAR2) 2 32 bits 95 R/W Base Transfer Counter Register (BTCR2) 2 8 bits 96 R/W Base Address Register (BAR2) 2 32 bits 97 R/W Base Address Register (BAR2) 2 32 bits 98 R/W Base Transfer Counter Register (BTCR2) 2 8 bits 97 R/W Base Address Register (BAR2) 2 32 bits 80 R/W Channel Status Register (CER2) 2 8 bits 80 R/W Device Control Register (CER2) 2 8 bits 81 R Channel Error Register (CER2) 2 8 bits 84 R/W Device Control Register (CER2) 2 8 bits 85 R/W Operation Control Register (CCR2) 2 8 bits 86 R/W Sequence Control Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 80 R/W Channel Priority Register (CCR2) 2 8 bits 80 R/W Channel Priority Register (CCR2) 2 8 bits 80 R/W Channel Priority Re |                                |      |                                  |         |                |         |

| 54 R/W Device Address Register (DAR1) 1 32 bits 54 R/W Device Function Code Register (DFCR1) 1 8 bits 55 A R/W Base Transfer Counter Register (BTCR1) 1 16 bits 55 C R/W Base Address Register (BAR1) 1 32 bits 79 R/W Base Address Register (BAR1) 1 32 bits 79 R/W Base Function Code Register (BFCR1) 1 8 bits 40 R/W Channel Status Register (CSR1) 1 8 bits 41 R Channel Error Register (CER1) 1 8 bits 44 R/W Device Control Register (DCR1) 1 8 bits 45 R/W Operation Control Register (OCR1) 1 8 bits 46 R/W Sequence Control Register (OCR1) 1 8 bits 46 R/W Sequence Control Register (CCR1) 1 8 bits 47 R/W Channel Priority Register (CCR1) 1 8 bits 60 R/W Channel Priority Register (CPR1) 1 8 bits 67 R/W Channel Priority Register (CPR1) 1 8 bits 67 R/W Error Interrupt Vector Register (MIVR1) 1 8 bits 67 R/W Error Interrupt Vector Register (MTCR2) 2 32 bits 80 R/W Memory Address Register (MTCR2) 2 32 bits 94 R/W Device Address Register (MFCR2) 2 32 bits 94 R/W Device Address Register (DAR2) 2 32 bits 94 R/W Device Function Code Register (MFCR2) 2 8 bits 94 R/W Base Transfer Counter Register (BTCR2) 2 16 bits 96 R/W Base Transfer Counter Register (BTCR2) 2 16 bits 97 R/W Base Address Register (BAR2) 2 32 bits 98 R/W Base Transfer Counter Register (BAR2) 2 32 bits 98 R/W Base Transfer Counter Register (BAR2) 2 32 bits 98 R/W Base Transfer Counter Register (BAR2) 2 32 bits 98 R/W Base Transfer Counter Register (BAR2) 2 32 bits 98 R/W Base Transfer Counter Register (BAR2) 2 32 bits 98 R/W Base Transfer Counter Register (BAR2) 2 32 bits 98 R/W Base Function Code Register (BAR2) 2 32 bits 80 R/W Channel Status Register (CSR2) 2 8 bits 81 R Channel Error Register (CCR2) 2 8 bits 85 R/W Operation Control Register (CCR2) 2 8 bits 86 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 87 R/W Channel Priority Register (CCR2) 2 8 bits 80 R/W Channel Prio |                                |      |                                  |         |                | 8 bits  |