#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

#### **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

PCI-DIO-96

# **DAQ**

#### PCI-DIO-96/PXI-6508/PCI-6503 User Manual

96-Bit and 24-Bit Parallel Digital I/O Interface for PCI, PXI, and CompactPCI

#### **Worldwide Technical Support and Product Information**

ni.com

#### National Instruments Corporate Headquarters

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

#### **Worldwide Offices**

Australia 1800 300 800, Austria 43 662 457990-0, Belgium 32 (0) 2 757 0020, Brazil 55 11 3262 3599, Canada 800 433 3488, China 86 21 5050 9800, Czech Republic 420 224 235 774, Denmark 45 45 76 26 00, Finland 358 (0) 9 725 72511, France 01 57 66 24 24, Germany 49 89 7413130, India 91 80 41190000, Israel 972 3 6393737, Italy 39 02 41309277, Japan 0120-527196, Korea 82 02 3451 3400, Lebanon 961 (0) 1 33 28 28, Malaysia 1800 887710, Mexico 01 800 010 0793, Netherlands 31 (0) 348 433 466, New Zealand 0800 553 322, Norway 47 (0) 66 90 76 60, Poland 48 22 328 90 10, Portugal 351 210 311 210, Russia 7 495 783 6851, Singapore 1800 226 5886, Slovenia 386 3 425 42 00, South Africa 27 0 11 805 8197, Spain 34 91 640 0085, Sweden 46 (0) 8 587 895 00, Switzerland 41 56 2005151, Taiwan 886 02 2377 2222, Thailand 662 278 6777, Turkey 90 212 279 3031, United Kingdom 44 (0) 1635 523545

For further support information, refer to the *Technical Support and Professional Services* appendix. To comment on National Instruments documentation, refer to the National Instruments Web site at ni.com/info and enter the info code feedback.

© 2006–2009 National Instruments Corporation. All rights reserved.

# **Important Information**

#### Warranty

The PCI-DIO-96, PXI-6508, and PCI-6503 are warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

Except as specified herein, National Instruments makes no warranties, express or implied, and specifically disclaims any warranty of merchantability or fitness for a particular purpose. Customer's right to recover damages caused by fault or negligence on the part of National Instruments shall be limited to the amount therefore paid by the customer. National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

National Instruments respects the intellectual property of others, and we ask our users to do the same. NI software is protected by copyright and other intellectual property laws. Where NI software may be used to reproduce software or other materials belonging to others, you may use NI software only to reproduce materials that you may reproduce in accordance with the terms of any applicable license or other legal restriction.

#### **Trademarks**

National Instruments, NI, ni.com, and LabVIEW are trademarks of National Instruments Corporation. Refer to the *Terms of Use* section on ni.com/legal for more information about National Instruments trademarks.

Other product and company names mentioned herein are trademarks or trade names of their respective companies.

Members of the National Instruments Alliance Partner Program are business entities independent from National Instruments and have no agency, partnership, or joint-venture relationship with National Instruments.

#### **Patents**

For patents covering National Instruments products/technology, refer to the appropriate location: **Help»Patents** in your software, the patents.txt file on your media, or the *National Instruments Patent Notice* at ni.com/patents.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CAN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY, COMPUTER OPERATING SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED "SYSTEM FAILURES"). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILY INJURY AND DEATH), SHOULD NOT BE RELIANT SOLELY UPON ONE FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS. BECAUSE EACH END-USER SYSTEM IS CUSTOMIZED AND DIFFERS FROM NATIONAL INSTRUMENTS TESTING PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS PRODUCTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATION THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

# **Contents**

| Abou   | t This Manual                                        |

|--------|------------------------------------------------------|

|        | Conventionsix                                        |

|        | Related Documentationx                               |

| Chap   | ter 1                                                |

| -      | duction                                              |

|        | About Your Board1-1                                  |

|        | Using PXI with CompactPCI                            |

|        | What You Need to Get Started                         |

|        | Optional Equipment                                   |

|        | Custom Cabling                                       |

|        | Unpacking                                            |

| Chan   | iter 2                                               |

| _      |                                                      |

| IIISta | llation and Configuration                            |

|        | Software Installation                                |

|        | Installing NI-DAQ2-1                                 |

|        | Installing Other Software2-1                         |

|        | Hardware Installation2-1                             |

|        | Installing the PCI-DIO-96 or PCI-6503                |

|        | Installing the PXI-6508                              |

|        | Board Configuration                                  |

| Chap   | ter 3                                                |

| Sign   | al Connections                                       |

|        | I/O Connector (PCI-DIO-96, PXI-6508)                 |

|        | I/O Connector Pin Assignments                        |

|        | Cable Assembly Connectors3-3                         |

|        | I/O Connector Signal Descriptions                    |

|        | I/O Connector (PCI-6503)                             |

|        | PCI-6503 I/O Connector Pin Descriptions3-6           |

|        | Port C Pin Assignments                               |

|        | Digital I/O Signal Connections                       |

|        | Power Connections                                    |

|        | Digital I/O Power-up State Selection3-10             |

|        | High DIO Power-up State3-10                          |

|        | Low DIO Power-up State (PXI-6508, PCI-6503 Only)3-12 |

# Chapter 4 Theory of Operation

| Functional Overview                      | 4-1 |

|------------------------------------------|-----|

| PCI Interface Circuitry                  | 4-3 |

| 82C55A Programmable Peripheral Interface |     |

| Timing Specifications                    |     |

| Mode 1 Input Timing                      |     |

| Mode 1 Output Timing                     |     |

| Mode 2 Bidirectional Timing              |     |

| č                                        |     |

# Appendix A Specifications

# Appendix B

## **Register-Level Programming**

| 82C53 Programmable Interval Timer (PCI-DIO-96, PXI-6508 Only) | B-2  |

|---------------------------------------------------------------|------|

| Interrupt Control Circuitry                                   | B-2  |

| Register Map and Description                                  | B-4  |

| Introduction                                                  | B-4  |

| Register Map                                                  | B-5  |

| Register Descriptions                                         |      |

| Register Description Format                                   | B-6  |

| Register Description for the 82C55A                           | B-6  |

| Register Description for the 82C53                            |      |

| (PCI-DIO-96, PXI-6508 Only)                                   |      |

| Register Description for the Interrupt Control Registers      |      |

| Interrupt Control Register 1                                  |      |

| Interrupt Control Register 2                                  | B-12 |

| Interrupt Clear Register (PCI-DIO-96, PXI-6508 Only)          | B-13 |

| Programming                                                   | B-14 |

| PCl Local Bus                                                 | B-14 |

| Programming Examples                                          | B-14 |

| PCI Initialization                                            | B-15 |

| Programming Considerations for the 82C55A                     | B-17 |

| Modes of Operation                                            | B-17 |

| Mode 0—Basic I/O                                              | B-18 |

| Mode 1—Strobed Input                                          | B-19 |

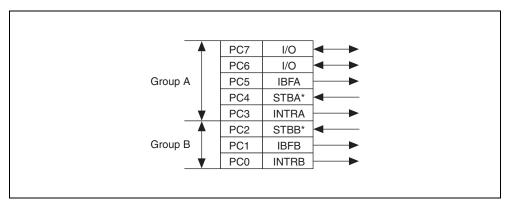

| Port C Status-Word Bit Definitions for Input (Ports A and B)  | B-21 |

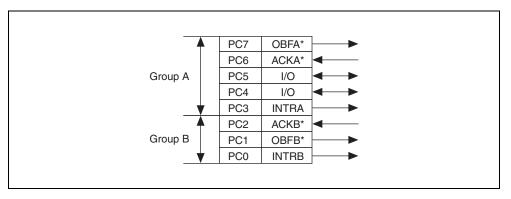

| Mode 1—Strobed Output                                         | B-23 |

| Port C Status-Word Bit Definitions for Output (Ports A and B) | B-24 |

| Mode 2—Bidirectional Bus                                      | B-26 |

|                              | Port C Status-Word Bit Definitions for Bidirectional    |      |

|------------------------------|---------------------------------------------------------|------|

|                              | Data Path (Port A Only)                                 |      |

| Inte                         | errupt Handling                                         |      |

|                              | Interrupt Programming Examples for the 82C55A           |      |

| Pro                          | gramming Considerations for the 82C53                   | B-30 |

|                              | General Information                                     |      |

|                              | Interrupt Programming Example                           | B-31 |

| Appendix C<br>Technical Supp | ort and Professional Services                           |      |

| Glossary                     |                                                         |      |

| Index                        |                                                         |      |

| Figures                      |                                                         |      |

| Figure 3-1.                  | PCI-DIO-96 and PXI-6508 Connector Pin Assignments       | 3-2  |

| Figure 3-2.                  | Cable-Assembly Connector Pinout for the R1005050        |      |

| 118410 0 2.                  | Ribbon Cable (PCI-DIO-96 and PXI-6508)                  | 3-3  |

| Figure 3-3.                  | PCI-6503 I/O Connector Pin Assignments                  |      |

| Figure 3-4.                  | Digital I/O Connections Block Diagram                   |      |

| Figure 3-5.                  | DIO Channel Configured for High DIO Power-up            |      |

| S                            | State with External Load                                | 3-11 |

| Figure 3-6.                  | DIO Channel Configured for Low DIO Power-up             |      |

| <i>G</i>                     | State with External Load                                | 3-12 |

| Figure 4-1.                  | PCI-DIO-96/PXI-6508 Block Diagram                       | 4-2  |

| Figure 4-2.                  | Timing Specifications for Mode 1 Input Transfer         |      |

| Figure 4-3.                  | Timing Specifications for Mode 1 Output Transfer        |      |

| Figure 4-4.                  | Timing Specifications for Mode 2 Bidirectional Transfer |      |

| Figure B-1.                  | Interrupt Control Circuitry Block Diagram               | B-3  |

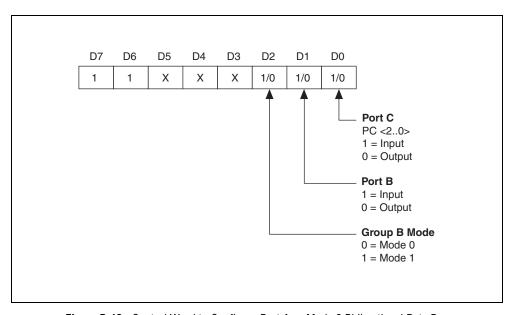

| Figure B-2.                  | Control Word Formats for the 82C55A                     |      |

| Figure B-3.                  | Control Word Format for the 82C53                       | B-9  |

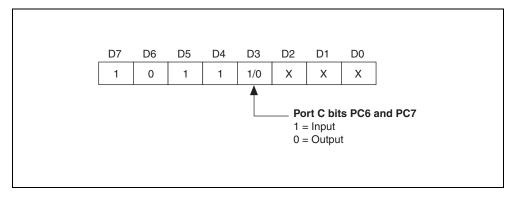

| Figure B-4.                  | Control Word to Configure Port A for Mode 1 Input       | B-19 |

| Figure B-5.                  | Control Word to Configure Port B for Mode 1 Input       |      |

| Figure B-6.                  | Port C Pin Assignments on I/O Connector when Port C     |      |

| -                            | Configured for Mode 1 Input                             | B-22 |

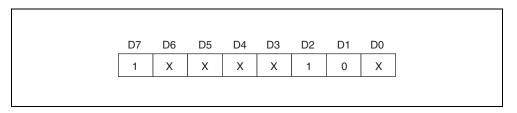

| Figure B-7.                  | Control Word to Configure Port A for Mode 1 Output      |      |

| Figure B-8.                  | Control Word to Configure Port B for Mode 1 Output      |      |

| Figure B-9.                  | Port C Pin Assignments on I/O Connector when Port C     |      |

Configured for Mode 1 Output.....B-25

|       | Figure B-10. | Control Word to Configure Port A as Mode 2             | D 26 |

|-------|--------------|--------------------------------------------------------|------|

|       | E' D 11      | Bidirectional Data Bus                                 | B-26 |

|       | Figure B-11. | Port C Pin Assignments on I/O Connector when Port C is | D 20 |

|       |              | Configured for Mode 2                                  | B-28 |

| Table | S            |                                                        |      |

|       | Table 3-1.   | Signal Descriptions for PCI-DIO-96 and                 |      |

|       |              | PXI-6508 I/O Connectors                                | 3-4  |

|       | Table 3-2.   | PCI-6503 Signal Descriptions                           | 3-7  |

|       | Table 3-3.   | Port C Signal Assignments                              |      |

|       | Table 4-1.   | The 82C55A Chips Used in the PCI-DIO-96, PXI-6508,     |      |

|       |              | and PCI-6503                                           | 4-3  |

|       | Table 4-2.   | Signal Names Used in Timing Diagrams                   | 4-4  |

|       | Table B-1.   | Register Address Map                                   | B-5  |

|       | Table B-2.   | Port C Set/Reset Control Words                         | B-8  |

|       | Table B-3.   | Common Programming Example Terms                       | B-15 |

|       | Table B-4.   | Mode 0 I/O Configurations                              |      |

# **About This Manual**

This manual describes the electrical and mechanical aspects of the PCI-DIO-96, PXI-6508, and PCI-6503 and contains information concerning their installation, operation, and programming. The PCI-DIO-96 and PCI-6503 are members of the National Instruments PCI Series of expansion boards for PCI bus computers. The PXI-6508 is a member of the National Instruments PXI family of expansion boards for PXI and CompactPCI chassis. These boards are designed for high-performance data acquisition and control for applications in laboratory testing, production testing, and industrial process monitoring and control.

#### **Conventions**

The following conventions are used in this manual:

Angle brackets that contain numbers separated by an ellipsis represent a range of values associated with a bit or signal name—for example,

AO <3..0>.

The » symbol leads you through nested menu items and dialog box options to a final action. The sequence **File»Page Setup»Options** directs you to pull down the **File** menu, select the **Page Setup** item, and select **Options**

from the last dialog box.

This icon to the left of bold italicized text denotes a note, which alerts you

to important information.

This icon to the left of bold italicized text denotes a caution, which advises you of precautions to take to avoid injury, data loss, or a system crash.

Bold text denotes items that you must select or click in the software, such

as menu items and dialog box options. Bold text also denotes parameter

names.

Italic text denotes variables, emphasis, a cross-reference, or an introduction

to a key concept. Italic text also denotes text that is a placeholder for a word

or value that you must supply.

bold

<>

monospace

Text in this font denotes text or characters that you should enter from the keyboard, sections of code, programming examples, and syntax examples. This font is also used for the proper names of disk drives, paths, directories, programs, subprograms, subroutines, device names, functions, operations, variables, filenames, and extensions.

PPIx

PPI *x*, where the *x* is replaced by A, B, C, or D, refers to one of the four programmable peripheral interface (PPI) chips on the PCI-DIO-96 or PXI-6508. The PCI-6503 contains only one PPI, PPI A.

Your DIO board

Your DIO board refers to either the PCI-DIO-96, PXI-6508, or PCI-6503 board.

#### **Related Documentation**

The following National Instruments document contains information that you may find helpful as you read this manual.

- Field Wiring and Noise Considerations for Analog Signals—To access this document, go to ni.com/info and enter the info code rdfwin.

- PCI Local Bus Specification, Revision 2.1

- National Instruments *PXI Specification*, Revision 1.0

- PICMG 2.0 R2.1 CompactPCI

- Software documentation—Examples of software documentation you may have are the LabVIEW or LabWindows™/CVI™ documentation sets and the NI-DAQmx or Traditional NI-DAQ (Legacy) documentation. After you set up your hardware system, use either the application software or the NI-DAQ documentation to help you write your application. If you have a large and complicated system, it is worthwhile to look through the software documentation before you configure your hardware.

- Accessory installation guides or manuals—If you are using accessory

products, read the terminal block and cable assembly installation

guides or accessory board user manuals. They explain how to

physically connect the relevant pieces of the system. Consult these

guides when you are making your connections.

Introduction

This chapter describes the PCI-DIO-96, PXI-6508, and PCI-6503; lists what you need to get started, software programming choices, and optional equipment; describes custom cabling options; and explains how to unpack your board.

#### **About Your Board**

Thank you for purchasing a National Instruments PCI-DIO-96, PXI-6508, or PCI-6503 board. The PCI-DIO-96 is a 96-bit, parallel, digital I/O interface for PCI bus computers. The PXI-6508 is a 96-bit, parallel, digital I/O interface for PXI and CompactPCI chassis. The PCI-6503 is a 24-bit, parallel, digital I/O interface for PCI bus computers.

Four 82C55A programmable peripheral interface (PPI) chips control the 96 bits of TTL-compatible digital I/O on the PCI-DIO-96 or PXI-6508. On the PCI-6503, one 82C55A PPI controls the 24 bits of TTL-compatible digital I/O. The 82C55A PPI chips can operate in unidirectional mode, bidirectional mode, or handshaking mode and can generate interrupt requests to your computer. The digital I/O lines are all accessible through a 100-pin female connector on the PCI-DIO-96 or PXI-6508 and a 50-pin male connector on the PCI-6503.

Your DIO board is a completely switchless and jumperless DAQ board. All resource allocation is completed automatically at startup, so you will not need to set interrupt levels or base addresses.

With your DIO board, you can use your computer as a digital I/O system controller for laboratory testing, production testing, and industrial process monitoring and control.

Detailed PCI-DIO-96, PXI-6508, and PCI-6503 specifications are in Appendix A, *Specifications*.

## **Using PXI with CompactPCI**

Using PXI-compatible products with standard CompactPCI products is an important feature provided by the *PXI Specification*, Revision 1.0. If you use a PXI-compatible plug-in device in a standard CompactPCI chassis you can use the basic plug-in device functions, but the PXI-specific functions will be unavailable.

The CompactPCI specification permits vendors to develop sub-buses that coexist with the basic PCI interface on the CompactPCI bus. Compatible operation is not guaranteed between CompactPCI devices with different sub-buses nor between CompactPCI devices with sub-buses and PXI. The standard implementation for CompactPCI does not include these sub-buses. Your PXI-6508 device works in any standard CompactPCI chassis adhering to the *PICMG 2.0 R2.1 CompactPCI* core specification.

#### What You Need to Get Started

| set up and use your PCI-DIO-96/PXI-6508/PCI-6503 board, you will d the following: |

|-----------------------------------------------------------------------------------|

| PCI-DIO-96, PXI-6508, or PCI-6503 board                                           |

| PCI-DIO-96/PXI-6508/PCI-6503 User Manual                                          |

| One of the following software packages and documentation:                         |

| – LabVIEW                                                                         |

| <ul><li>LabWindows/CVI</li></ul>                                                  |

| - NI-DAQmx                                                                        |

| <ul> <li>Traditional NI-DAQ (Legacy)</li> </ul>                                   |

| <ul> <li>Measurement Studio</li> </ul>                                            |

| Your computer, or PXI or CompactPCI chassis and controller                        |

## **Optional Equipment**

National Instruments offers a variety of products to use with your DIO board, including cables, connector blocks, and other accessories, as follows:

- Cables and cable assemblies

- Connector blocks, 50-pin screw terminals

- SCXI modules and accessories for isolating, amplifying, exciting, and multiplexing signals for relays and analog output. With SCXI you can condition and acquire up to 3,072 channels.

- Low channel count signal conditioning modules, boards, and accessories, including conditioning for strain gauges and RTDs, simultaneous sample and hold, and relays

For more information about optional equipment available from National Instruments, visit ni.com.

## **Custom Cabling**

**Caution** For compliance with Electromagnetic Compatibility (EMC) requirements, this product must be operated with shielded cables and accessories. If unshielded cables or accessories are used, the EMC specifications are no longer guaranteed unless all unshielded cables and/or accessories are installed in a shielded enclosure with properly designed and shielded input/output ports.

National Instruments offers cables and accessories for you to prototype your application or to use if you frequently change board interconnections.

If you want to develop your own cable, the mating connector for the PCI-DIO-96 and PXI-6508 is a 100-position, right-angle receptacle without board locks. Recommended manufacturer part numbers for this mating connector are as follows:

- AMP Corporation (part number 749879-9)

- Honda Corporation (part number PCS-XE100LFD-HS)

The mating connector for the PCI-6503 is a 50-position, polarized ribbon socket connector with strain relief. National Instruments uses a polarized (keyed) connector to prevent inadvertent upside-down connections. Recommended manufacturer part numbers for this mating connector are as follows:

- Electronic Products Division/3M (part number 3425-7650)

- T&B/Ansley Corporation (part number 622-5041)

### Unpacking

Your DIO board is shipped in an antistatic package to prevent electrostatic damage to the board. Electrostatic discharge can damage several components on the board. To avoid such damage in handling the board, take the following precautions:

- Ground yourself via a grounding strap or by holding a grounded object.

- Touch the antistatic package to a metal part of your computer chassis before removing the board from the package.

- Remove the board from the package and inspect the board for loose components or any other sign of damage. Notify National Instruments if the board appears damaged in any way. Do *not* install a damaged board into your computer.

- *Never* touch the exposed pins of connectors.

# **Installation and Configuration**

This chapter describes how to install and configure your PCI-DIO-96, PXI-6508, or PCI-6503 board.

#### **Software Installation**

Before installing your DIO device, you must install the software you plan to use with the device.

If you are a register-level programmer, refer to Appendix B, *Register-Level Programming*, of this manual.

#### Installing NI-DAQ

The *DAQ Getting Started Guide*, which you can download at ni.com/manuals, offers NI-DAQ users step-by-step instructions for installing software and hardware, configuring channels and tasks, and getting started developing an application.

#### **Installing Other Software**

If you are using other software, refer to the installation instructions that accompany your software.

#### **Hardware Installation**

The following sections contain general installation instructions for each device. Consult your computer or chassis user manual or technical reference manual for specific instructions about installing new devices in your computer or chassis.

#### Installing the PCI-DIO-96 or PCI-6503

To install a PCI-DIO-96 or PCI-6503 in any available 5 V PCI expansion slot in your computer, complete the following steps:

- 1. Turn off and unplug your computer.

- 2. Remove the top cover or access port to the expansion slots.

- 3. Remove the expansion slot cover on the back panel of the computer.

- 4. Touch the metal part inside your computer to discharge any static electricity that might be on your clothes or body.

- 5. Insert the PCI-DIO-96 or PCI-6503 in a 5 V PCI slot. It may be a tight fit, but do *not* force the device into place.

- 6. Screw the mounting bracket of the PCI-DIO-96 or PCI-6503 to the back panel rail of the computer.

- 7. Visually verify the installation.

- 8. Replace the top cover of your computer.

- 9. Plug in and turn on your computer.

#### Installing the PXI-6508

To install a PXI-6508 in any available 5 V peripheral slot in your PXI or CompactPCI chassis, complete the following steps:

- 1. Turn off and unplug your PXI or CompactPCI chassis.

- 2. Choose an unused PXI or CompactPCI 5 V peripheral slot.

- 3. Remove the filler panel for the peripheral slot you have chosen.

- 4. Touch a metal part of your chassis to discharge any static electricity that might be on your clothes or body.

- 5. Insert the PXI-6508 in the selected 5 V slot. Use the injector/ejector handle to fully inject the device into place.

- 6. Screw the front panel of the PXI-6508 to the front panel mounting rails of the PXI or CompactPCI chassis.

- 7. Visually verify the installation.

- 8. Plug in and turn on the PXI or CompactPCI chassis.

## **Board Configuration**

Your DIO board is completely software configurable. The PCI-DIO-96 and PCI-6503 are fully compliant with the *PCI Local Bus Specification*, Revision 2.1, and the PXI-6508 is fully compliant with the *PXI Specification*, Revision 1.0. Therefore, all board resources are automatically allocated by the PCI system, including the base address and interrupt level. The base address of the board is mapped into PCI memory space. You do not need to perform any configuration steps after the system powers up.

# **Signal Connections**

This chapter describes how to make input and output signal connections to your PCI-DIO-96, PXI-6508, and PCI-6503 via the board I/O connector.

**Caution** Connections that exceed any of the maximum ratings of input or output signals on your DIO board can damage the board and your computer. The description of each signal in this chapter includes information about maximum input ratings. National Instruments is *not* liable for any damages resulting from signal connections that exceed these maximum ratings.

**Note** For information on adding signal conditioning into your applications and National Instruments signal conditioning devices, go to ni.com/signalconditioning.

## I/O Connector (PCI-DIO-96, PXI-6508)

The I/O connector for the PCI-DIO-96 and PXI-6508 has 100 pins that you can connect to 50-pin accessories with the R1005050 cable.

#### I/O Connector Pin Assignments

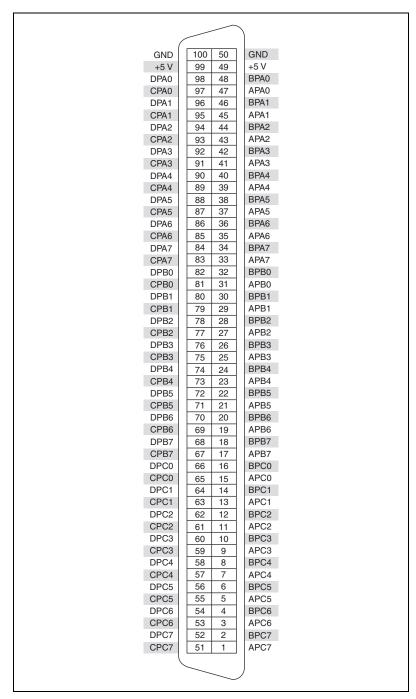

Figure 3-1 shows the pin assignments for the PCI-DIO-96 and PXI-6508 digital I/O connector.

Figure 3-1. PCI-DIO-96 and PXI-6508 Connector Pin Assignments

#### **Cable Assembly Connectors**

The optional R1005050 cable assembly you can use with the PCI-DIO-96 or PXI-6508 is an assembly of two 50-pin cables and three connectors. Both cables are joined to a single connector on one end and to individual connectors on the free ends. The 100-pin connector that joins the two cables plugs into the I/O connector of the PCI-DIO-96 and PXI-6508. The other two connectors are 50-pin connectors, one of which is connected to pins 1 through 50 and the other connected to pins 51 through 100 of the PCI-DIO-96 and PXI-6508 connector. Figure 3-2 shows the pin assignments for each of the 50-pin connectors on the cable assembly.

| Positions 1–50 |    |    |      | Pos  | itions | 51- | 100  |

|----------------|----|----|------|------|--------|-----|------|

| APC7           | 1  | 2  | BPC7 | CPC7 | 1      | 2   | DPC7 |

| APC6           | 3  | 4  | BPC6 | CPC6 | 3      | 4   | DPC6 |

| APC5           | 5  | 6  | BPC5 | CPC5 | 5      | 6   | DPC5 |

| APC4           | 7  | 8  | BPC4 | CPC4 | 7      | 8   | DPC4 |

| APC3           | 9  | 10 | BPC3 | CPC3 | 9      | 10  | DPC3 |

| APC2           | 11 | 12 | BPC2 | CPC2 | 11     | 12  | DPC2 |

| APC1           | 13 | 14 | BPC1 | CPC1 | 13     | 14  | DPC1 |

| APC0           | 15 | 16 | BPC0 | CPC0 | 15     | 16  | DPC0 |

| APB7           | 17 | 18 | BPB7 | CPB7 | 17     | 18  | DPB7 |

| APB6           | 19 | 20 | BPB6 | CPB6 | 19     | 20  | DPB6 |

| APB5           | 21 | 22 | BPB5 | CPB5 | 21     | 22  | DPB5 |

| APB4           | 23 | 24 | BPB4 | CPB4 | 23     | 24  | DPB4 |

| APB3           | 25 | 26 | врв3 | CPB3 | 25     | 26  | DPB3 |

| APB2           | 27 | 28 | BPB2 | CPB2 | 27     | 28  | DPB2 |

| APB1           | 29 | 30 | BPB1 | CPB1 | 29     | 30  | DPB1 |

| APB0           | 31 | 32 | BPB0 | CPB0 | 31     | 32  | DPB0 |

| APA7           | 33 | 34 | BPA7 | CPA7 | 33     | 34  | DPA7 |

| APA6           | 35 | 36 | BPA6 | CPA6 | 35     | 36  | DPA6 |

| APA5           | 37 | 38 | BPA5 | CPA5 | 37     | 38  | DPA5 |

| APA4           | 39 | 40 | BPA4 | CPA4 | 39     | 40  | DPA4 |

| APA3           | 41 | 42 | BPA3 | CPA3 | 41     | 42  | DPA3 |

| APA2           | 43 | 44 | BPA2 | CPA2 | 43     | 44  | DPA2 |

| APA1           | 45 | 46 | BPA1 | CPA1 | 45     | 46  | DPA1 |

| APA0           | 47 | 48 | BPA0 | CPA0 | 47     | 48  | DPA0 |

| +5 V           | 49 | 50 | GND  | +5 V | 49     | 50  | GND  |

**Figure 3-2.** Cable-Assembly Connector Pinout for the R1005050 Ribbon Cable (PCI-DI0-96 and PXI-6508)

## I/O Connector Signal Descriptions

Table 3-1 lists the signal descriptions for the PCI-DIO-96 and PXI-6508 I/O connector pins.

Table 3-1. Signal Descriptions for PCI-DIO-96 and PXI-6508 I/O Connectors

| Pin                               | Signal Name | Alternate<br>Port ID <sup>†</sup> | Description                                                                    |

|-----------------------------------|-------------|-----------------------------------|--------------------------------------------------------------------------------|

| 1, 3, 5, 7, 9, 11, 13, 15         | APC<70>     | 2                                 | Bidirectional data lines for port C of PPI A—APC7 is the MSB, APC0 is the LSB. |

| 2, 4, 6, 8, 10, 12, 14, 16        | BPC<70>     | 5                                 | Bidirectional data lines for port C of PPI B—BPC7 is the MSB, BPC0 is the LSB. |

| 17, 19, 21, 23, 25, 27, 29, 31    | APB<70>     | 1                                 | Bidirectional data lines for port B of PPI A—APB7 is the MSB, APB0 is the LSB. |

| 18, 20, 22, 24, 26, 28, 30, 32    | BPB<70>     | 4                                 | Bidirectional data lines for port B of PPI B—BPB7 is the MSB, BPB0 is the LSB. |

| 33, 35, 37, 39, 41, 43,<br>45, 47 | APA<70>     | 0                                 | Bidirectional data lines for port A of PPI A—APA7 is the MSB, APA0 is the LSB. |

| 34, 36, 38, 40, 42, 44,<br>46, 48 | BPA<70>     | 3                                 | Bidirectional data lines for port A of PPI B—BPA7 is the MSB, BPA0 is the LSB. |

| 49, 99                            | +5 V supply | _                                 | +5 Volts—These pins are fused for up to 1 A total of +4.65 to +5.25 V.         |

| 50, 100                           | GND         | _                                 | Ground—These pins are connected to the computer ground signal.                 |

| 51, 53, 55, 57, 59, 61,<br>63, 65 | CPC<70>     | 8                                 | Bidirectional data lines for port C of PPI C—CPC7 is the MSB, CPC0 is the LSB. |

| 52, 54, 56, 58, 60, 62,<br>64, 66 | DPC<70>     | 11                                | Bidirectional data lines for port C of PPI D—DPC7 is the MSB, DPC0 is the LSB. |

Table 3-1. Signal Descriptions for PCI-DIO-96 and PXI-6508 I/O Connectors (Continued)

| Pin                               | Signal Name | Alternate<br>Port ID <sup>†</sup> | Description                                                                    |

|-----------------------------------|-------------|-----------------------------------|--------------------------------------------------------------------------------|

| 67, 69, 71, 73, 75, 77,<br>79, 81 | CPB<70>     | 7                                 | Bidirectional data lines for port B of PPI C—CPB7 is the MSB, CPB0 is the LSB. |

| 68, 70, 72, 74, 76, 78,<br>80, 82 | DPB<70>     | 10                                | Bidirectional data lines for port B of PPI D—DPB7 is the MSB, DPB0 is the LSB. |

| 83, 85, 87, 89, 91, 93, 95, 97    | CPA<70>     | 6                                 | Bidirectional data lines for port A of PPI C—CPA7 is the MSB, CPA0 is the LSB. |

| 84, 86, 88, 90, 92, 94,<br>96, 98 | DPA<70>     | 9                                 | Bidirectional data lines for port A of PPI D—DPA7 is the MSB, DPA0 is the LSB. |

<sup>†</sup> This document refers to the ports as A, B, and C and the PPIs (82C55As) as A, B, C, and D. NI-DAQmx, Traditional NI-DAQ (Legacy), and LabVIEW documentation use numbers to identify each port and PPI. For example, this manual uses PPI A port A to refer to port A of the 82C55A identified as PPI A. NI-DAQmx, Traditional NI-DAQ (Legacy), LabWindows/CVI, LabVIEW, or other application software documentation, however, refer to this port as  $\theta$ . The Alternate Port ID column shows the correlation between the different port names.

# I/O Connector (PCI-6503)

The PCI-6503 has 50 pins that you can connect to 50-pin accessories with the NB1 cable.

#### PCI-6503 I/O Connector Pin Descriptions

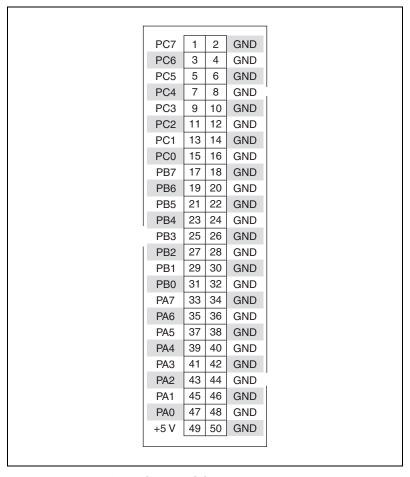

Figure 3-3 shows the pin assignments for the PCI-6503 digital I/O connector using the NB1 ribbon cable.

Figure 3-3. PCI-6503 I/O Connector Pin Assignments

Table 3-2 describes the PCI-6503 signals.

**Table 3-2.** PCI-6503 Signal Descriptions

| Pin                               | Signal Name | Alternate<br>Port ID <sup>†</sup> | Description                                                                 |

|-----------------------------------|-------------|-----------------------------------|-----------------------------------------------------------------------------|

| 1, 3, 5, 7, 9, 11, 13, 15         | PC<70>      | 2                                 | Port C—Bidirectional data lines for port C. PC7 is the MSB, PC0 is the LSB. |

| 17, 19, 21, 23, 25, 27, 29, 31    | PB<70>      | 1                                 | Port B—Bidirectional data lines for port B. PB7 is the MSB, PB0 is the LSB. |

| 33, 35, 37, 39, 41, 43,<br>45, 47 | PA<70>      | 0                                 | Port A—Bidirectional data lines for port B. PA7 is the MSB, PA0 is the LSB. |

| 49                                | +5 V        | _                                 | +5 Volts—This pin is fused for up to 1 A at +4.65 to 5.25 V.                |

| All even-numbered pins            | GND         | _                                 | Ground—These signals are connected to the computer ground reference.        |

<sup>&</sup>lt;sup>†</sup> This document refers to the 82C55 ports as A, B, and C. NI-DAQmx, Traditional NI-DAQ (Legacy), and LabVIEW documentation use numbers to identify ports. For example, this manual uses port A to refer to the first port of the 82C55A. NI-DAQmx, Traditional NI-DAQ (Legacy), LabWindows/CVI, LabVIEW, or other application software documentation, however, refer to this port as 0. The Alternate Port ID column shows the correlation between the different port names.

## **Port C Pin Assignments**

The signals assigned to port C vary depending on how the 82C55A is configured. In mode 0—or no handshaking configuration—port C is configured as two 4-bit I/O ports. In modes 1 and 2—or handshaking configuration—port C is used for status and handshaking signals with any leftover lines available for general-purpose I/O. Table 3-3 summarizes the port C signal assignments for each configuration. You can also use ports A and B in different modes; the table does not show every possible combination. Consult Appendix B, *Register-Level Programming*, for register-level programming information.

**Note** Table 3-3 shows both the port C signal assignments and the terminology correlation between different documentation sources. The 82C55A terminology refers to the different 82C55A configurations as modes whereas NI-DAQmx, Traditional NI-DAQ (Legacy), LabWindows/CVI, and LabVIEW documentation refers to them as handshaking and no handshaking. On the PCI-DIO-96 and PXI-6508, these signal assignments are the same for all four 82C55A PPIs. Refer to Table 3-1 for more information.

Table 3-3. Port C Signal Assignments

| Configuration Terminology                                      |                                     | Signal Assignments                    |                                       |                                       |                                       |                                       |                                       |                                       |                                       |

|----------------------------------------------------------------|-------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| 82C55A/<br>PCI-DIO-96/<br>PXI-6508/<br>PCI-6503<br>User Manual | National<br>Instruments<br>Software | APC7,<br>BPC7,<br>CPC7,<br>or<br>DPC7 | APC6,<br>BPC6,<br>CPC6,<br>or<br>DPC6 | APC5,<br>BPC5,<br>CPC5,<br>or<br>DPC5 | APC4,<br>BPC4,<br>CPC4,<br>or<br>DPC4 | APC3,<br>BPC3,<br>CPC3,<br>or<br>DPC3 | APC2,<br>BPC2,<br>CPC2,<br>or<br>DPC2 | APC1,<br>BPC1,<br>CPC1,<br>or<br>DPC1 | APC0,<br>BPC0,<br>CPC0,<br>or<br>DPC0 |

| Mode 0<br>(Basic I/O)                                          | No<br>Handshaking                   | I/O                                   |

| Mode 1<br>(Strobed Input)                                      | Handshaking                         | I/O                                   | I/O                                   | $IBF_A$                               | STB <sub>A</sub> *                    | INTR <sub>A</sub>                     | STB <sub>B</sub> *                    | $IBFB_{B}$                            | INTR <sub>B</sub>                     |

| Mode 1<br>(Strobed<br>Output)                                  | Handshaking                         | OBF <sub>A</sub> *                    | ACK <sub>A</sub> *                    | I/O                                   | I/O                                   | INTR <sub>A</sub>                     | ACK <sub>B</sub> *                    | OBF <sub>B</sub> *                    | INTR <sub>B</sub>                     |

| Mode 2<br>(Bidirectional<br>Bus)                               | Handshaking                         | OBF <sub>A</sub> *                    | ACK <sub>A</sub> *                    | $IBF_A$                               | STB <sub>A</sub> *                    | INTR <sub>A</sub>                     | I/O                                   | I/O                                   | I/O                                   |

**Notes**: Indicates that the signal is active low.

Subscripts A and B denote port A or port B handshaking signals.

## **Digital I/O Signal Connections**

Pins 1 through 48 and, on the PCI-DIO-96 and PXI-6508, pins 51 through 98 of the I/O connector are digital I/O signal pins. The following specifications and ratings apply to the digital I/O lines. The maximum input logic high and output logic high voltages assume a  $V_{\rm cc}$  supply voltage of 5.0 V.

The absolute maximum voltage rating is -0.5 to +5.5 V with respect to GND. For more information on the digital I/O signal specifications, refer to Appendix A, *Specifications*.

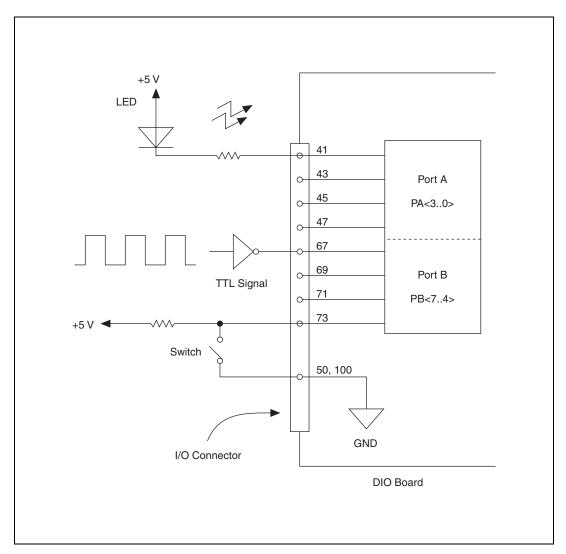

Figure 3-4 depicts signal connections for three typical digital I/O applications.

Figure 3-4. Digital I/O Connections Block Diagram

In Figure 3-4, port A of one PPI is configured for digital output, and port B is configured for digital input. Digital input applications include receiving TTL signals and sensing external device states such as the state of the switch in Figure 3-4. Digital output applications include sending TTL signals and driving external devices such as the LED shown in Figure 3-4.

#### **Power Connections**

Pin 49 and, on the PCI-DIO-96 and PXI-6508, pin 99 of the I/O connector supply +5 V from the computer power supply via a self-resetting fuse. The fuse resets automatically within a few seconds after the overcurrent condition is removed. These pins are referenced to GND and can be used to power external digital circuitry.

Power rating...... 1 A at +4.65 to +5.25 V

**Caution** Never connect the +5 V power pins directly to ground or to any other voltage source on your DIO board or to any other device. Doing so can damage your DIO board and the computer. National Instruments is *not* liable for damage resulting from such a connection.

## Digital I/O Power-up State Selection

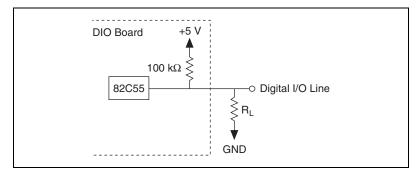

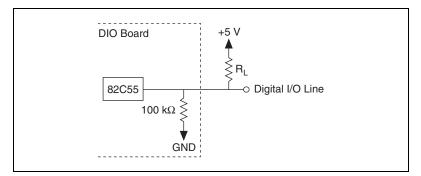

The PCI-DIO-96, PXI-6508, and PCI-6503 contain bias resistors that control the state of the digital I/O lines at power up. At power up, each digital I/O line is configured as an input, pulled either high or low by a  $100~\mathrm{k}\Omega$  bias resistor.

On the PCI-DIO-96, all of the 100 k $\Omega$  bias resistors pull up. Therefore, the default power-up state of each line on the PCI-DIO-96 is high.

On the PXI-6508 and PCI-6503, you can select the direction of the  $100\,\mathrm{k}\Omega$  bias resistors. Set jumper W1 to high to configure the resistors as pull-up resistors. Set jumper W1 to low to configure the resistors as pull-down resistors.

You can change individual lines from pulled up to pulled down—or, on the PXI-6508 and PCI-6503, from pulled down to pulled up—by adding your own external resistors. This section describes the procedure.

#### **High DIO Power-up State**

If you select the pulled-high mode, each DIO line is pulled to  $V_{cc}$  (approximately +5 VDC) with a  $100\,\mathrm{k}\Omega$  resistor. To pull a specific line low, connect between that line and ground a pull-down resistor ( $R_L$ ) whose value will give you a maximum of 0.4 VDC. The DIO lines provide a maximum of 2.5 mA at 3.7 V in the high state. Using the largest possible resistor ensures that you do not use more current than necessary to perform the pull-down task.

However, ensure the resistor value is not so large that leakage current from the DIO line along with the current from the  $100 \text{ k}\Omega$  pull-up resistor drives the voltage at the resistor above a TTL low level of 0.4 VDC.

Figure 3-5. DIO Channel Configured for High DIO Power-up State with External Load

#### Example:

By default, all DIO lines are pulled high at power up. To pull one channel low, complete the following steps:

- 1. Install a load (R<sub>L</sub>). Remember that the smaller the resistance, the greater the current consumption and the lower the voltage.

- 2. Using the following formula, calculate the largest possible load to maintain a logic low level of 0.4 V and supply the maximum driving current:

$$V = I \times R_L \Rightarrow R_L = V/I,$$

where V = 0.4 V; Voltage across  $R_L$

I = 46  $\mu A$  + 10  $\mu A;$  4.6 V across the 100  $k\Omega$  pull-up resistor and 10  $\mu A$  maximum leakage current(except lines PC0 and PC3)

therefore  $R_L = 7.1 \text{ k}\Omega$ ; 0.4 V/56  $\mu$ A

This resistor value, 7.1 k $\Omega$ , provides a maximum of 0.4 V on the DIO line at power up. You can substitute smaller resistor values to lower the voltage or to provide a margin for  $V_{cc}$  variations and other factors. However, smaller values draw more current, leaving less drive current for other circuitry connected to this line. The 7.1 k $\Omega$  resistor reduces the amount of logic high source current by 0.4 mA with a 2.8 V output.

The maximum leakage current on most lines is  $10 \,\mu A$ . The maximum leakage current on the PC(0) and PC(3) lines is  $20 \,\mu A$ .

#### Low DIO Power-up State (PXI-6508, PCI-6503 Only)

If you select pulled-low mode, each DIO line will be pulled to GND (0 VDC) using a  $100 \text{ k}\Omega$  resistor. If you want to pull a specific line high, connect a pull-up resistor that will give you a minimum of 2.8 VDC. The DIO lines are capable of sinking a maximum of 2.5 mA at 0.4 V in the low state. Using the largest possible resistance value ensures that you do not use more current than necessary to perform the pull-up task.

Also, ensure the pull-up resistor value is not so large that leakage current from the DIO line along with the current from the 100 k $\Omega$  pull-down resistor brings the voltage at the resistor below a TTL high level of 2.8 VDC.

Figure 3-6. DIO Channel Configured for Low DIO Power-up State with External Load

#### Example:

Set jumper W1 to low, which means all DIO lines are pulled low at power up. To pull one channel high, complete the following steps:

- 1. Install a load (R<sub>L</sub>). Remember that the smaller the resistance, the greater the current consumption and the higher the voltage.

- Using the following formula, calculate the largest possible load to maintain a logic high level of 2.8 V and supply the maximum sink current:

$$V = I \times R_L \Rightarrow R_L = V/I$$

where V = 2.2 V; Voltage across  $R_L$

I = 28  $\mu$ A + 10  $\mu$ A; 2.8 V across the 100 k $\Omega$  pull-up resistor and 10  $\mu$ A maximum leakage current (except lines PC0 and PC3)

therefore  $R_L = 5.7 \text{ k}\Omega$ ; 2.2 V/38  $\mu\text{A}$

This resistor value, 5.7 k $\Omega$ , provides a maximum of 2.8 V on the DIO line at power up. You can substitute smaller resistor values to lower the voltage drop or to provide a margin for  $V_{CC}$  variations and other factors. However, smaller values draw more current, leaving less sink current for other circuitry connected to this line. The 5.7 k $\Omega$  resistor reduces the amount of a logic low sink current by 0.8 mA with a 0.4 V output.

# **Theory of Operation**

This chapter contains a functional overview of the PCI-DIO-96, PXI-6508, and PCI-6503 and explains the operation of each functional unit.

## **Functional Overview**

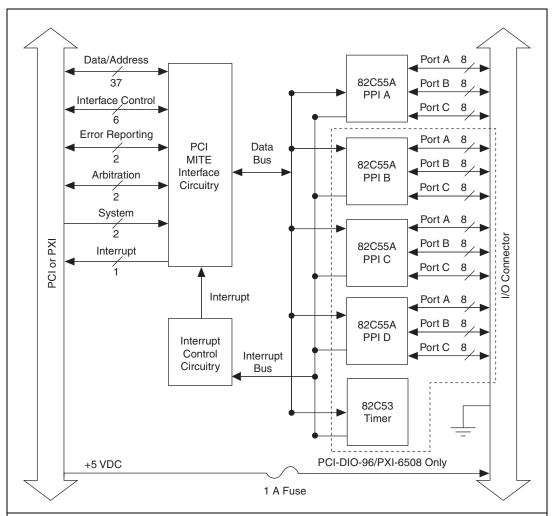

The block diagram in Figure 4-1 illustrates the key functional components of your DIO board.

**Note**: Current revisions of the NI PCI-DIO-96 and PXI-6508 no longer support the OKI 82C53 programmable interval timer. If you are using a PCI-DIO-96 revision G or earlier or PXI-6508 revision D or earlier, refer to Appendix B, *Register-Level Programming*, for more information about using the 82C53.

Figure 4-1. PCI-DIO-96/PXI-6508 Block Diagram

#### **PCI Interface Circuitry**

Your DIO board uses the PCI MITE ASIC to communicate with the PCI bus. The PCI MITE ASIC was designed by National Instruments specifically for data acquisition. The PCI MITE is fully compliant with *PCI Local Bus Specification*, Revision 2.1.

The base memory address and interrupt level for the board are stored inside the PCI MITE at power on. You do not need to set any switches or jumpers.

#### 82C55A Programmable Peripheral Interface

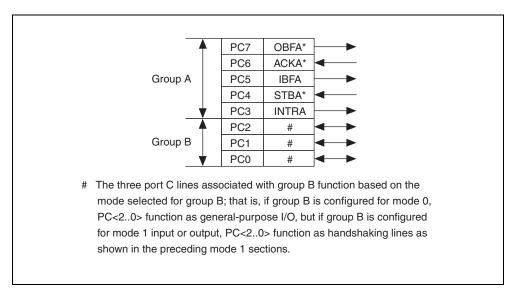

The 82C55A PPI chip is the heart of your DIO board. The PCI-DIO-96 and PXI-6508 contain four PPIs. The PCI-6503 contains one PPI. Each of these chips has 24 programmable I/O pins that represent three 8-bit ports: PA, PB, and PC. Each port can be programmed as an input or output port. The 82C55A has three modes of operation: simple I/O (mode 0), strobed I/O (mode 1), and bidirectional I/O (mode 2). In modes 1 and 2, the three ports are divided into two groups: group A and group B. Each group has eight data bits, plus control and status bits from port C (PC). Modes 1 and 2 use handshaking signals from the computer to synchronize data transfers. Refer to Appendix B, *Register-Level Programming*, for more detailed information.

Different revisions of the PCI-DIO-96, PXI-6508, and PCI-6503 use different 82C55A chips from Intersil Corporation or OKI Semiconductor. For the most recent data sheet for the Intersil CMS82C55A or CS82C55A, visit www.intersil.com. For the most recent data sheet for the OKI MSM82C55A, visit www2.okisemi.com.

Table 4-1 describes the 82C55A used in the PCI-DIO-96, PXI-6508, and PCI-6503.

| Type                  | Bus Hold† | PCI-DIO-96                           | PXI-6508                             | PCI-6503                             |

|-----------------------|-----------|--------------------------------------|--------------------------------------|--------------------------------------|

| Intersil<br>CMS82C55A | No        | Revision K or later                  | Revision G or later                  | Revision G or later                  |

| Intersil<br>CS82C55A  | Yes       | 182920H-01                           | 184836E-01                           | 185183E-01                           |

| OKI<br>MSM82C55A      | No        | 182920J-01,<br>revision G or earlier | 184836F-01,<br>revision D or earlier | 185183F-01,<br>revision D or earlier |

**Table 4-1.** The 82C55A Chips Used in the PCI-DIO-96, PXI-6508, and PCI-6503

<sup>†</sup> Indicates whether the chip has the bus hold feature on the port pins.

# **Timing Specifications**

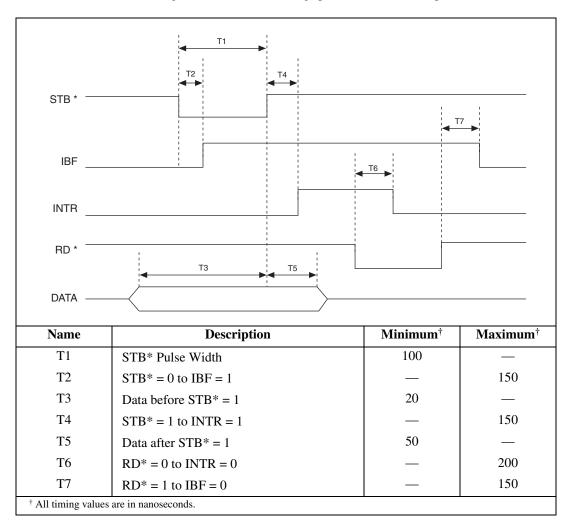

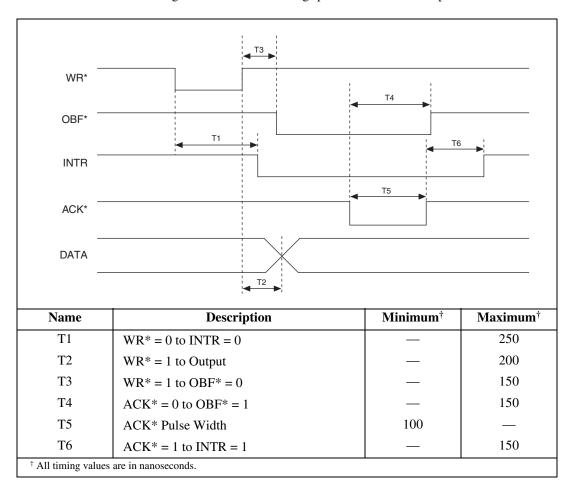

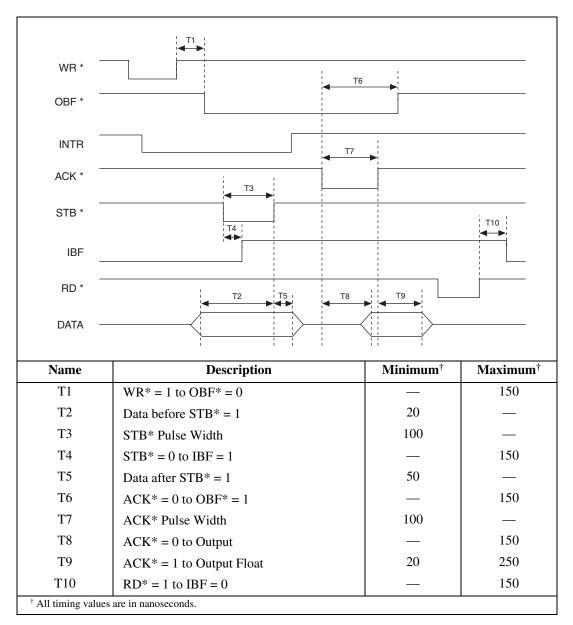

This section lists the timing specifications for handshaking with your DIO board. The handshaking lines STB\* and IBF synchronize input transfers. The handshaking lines OBF\* and ACK\* synchronize output transfers.

Table 4-2 describes signals appearing in the handshaking diagrams.

**Table 4-2.** Signal Names Used in Timing Diagrams

| Name | Type          | Description                                                                                                                                                                                                                             |

|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STB* | Input         | Strobe Input—A low signal on this handshaking line loads data into the input latch.                                                                                                                                                     |

| IBF  | Output        | Input Buffer Full—A high signal on this handshaking line indicates that data has been loaded into the input latch. A low signal indicates the board is ready for more data. This is an input acknowledge signal.                        |

| ACK* | Input         | Acknowledge Input—A low signal on this handshaking line indicates that the data written to the port has been accepted. This signal is a response from the external device indicating that it has received the data from your DIO board. |

| OBF* | Output        | Output Buffer Full—A low signal on this handshaking line indicates that data has been written to the port.                                                                                                                              |

| INTR | Output        | Interrupt Request—This signal becomes high when the 82C55A requests service during a data transfer. The appropriate interrupt enable bits must be set to generate this signal.                                                          |

| RD*  | Internal      | Read—This signal is the read signal generated from the control lines of the computer I/O expansion bus.                                                                                                                                 |

| WR*  | Internal      | Write—This signal is the write signal generated from the control lines of the computer I/O expansion bus.                                                                                                                               |

| DATA | Bidirectional | Data Lines at the Specified Port—For output mode, this signal indicates the availability of data on the data line. For input mode, this signal indicates when the data on the data lines should be valid.                               |

#### **Mode 1 Input Timing**

Figure 4-2 shows the timing specifications for an input transfer in mode 1.

Figure 4-2. Timing Specifications for Mode 1 Input Transfer

#### **Mode 1 Output Timing**

Figure 4-3 shows the timing specifications for an output transfer in mode 1.

Figure 4-3. Timing Specifications for Mode 1 Output Transfer

#### **Mode 2 Bidirectional Timing**

Figure 4-4 shows the timing specifications for bidirectional transfers in mode 2.

Figure 4-4. Timing Specifications for Mode 2 Bidirectional Transfer

# **Specifications**

This appendix lists the specifications for the PCI-DIO-96, PXI-6508, and PCI-6503. These specifications are typical at 25 °C unless otherwise noted.

# Digital I/O

| Number of channels PCI-DIO-96 and PXI-6508 PCI-6503 |                                                                                |

|-----------------------------------------------------|--------------------------------------------------------------------------------|

| Compatibility                                       | .TTL                                                                           |

| Power on state                                      |                                                                                |

| PCI-DIO-96                                          | . Inputs (high-Z), pulled up through $100~\mathrm{k}\Omega$                    |

| PXI-6508, PCI-6503                                  | Inputs (high-Z), pulled up or down through $100 \ k\Omega$ (jumper selectable) |

| Handshaking                                         | . Input, output, or bidirectional                                              |

| Data transfers                                      | . Interrupts, programmed I/O                                                   |

# **Digital Logic Levels**

# **Input Signals**

The maximum input logic high and output logic high voltages assume a  $V_{cc}$  supply voltage of 5.0 V. Given a  $V_{cc}$  supply voltage of 5.0 V, the absolute maximum voltage rating for each I/O line is -0.5 V to 5.5 V with respect to GND.

| Level                                                                                   | Min    | Max                 |

|-----------------------------------------------------------------------------------------|--------|---------------------|

| Input logic high voltage                                                                | 2.2 V  | 5.3 V               |

| Input logic low voltage                                                                 | -0.3 V | 0.8 V               |

| Input high current $(V_{in} = 5 \text{ V}, \text{ resistors set to pull-up}^{\dagger})$ |        | 10 μA <sup>‡</sup>  |

| Input high current $(V_{in} = 5 \text{ V, resistors set to pull-down}^{\dagger})$       | _      | 75 μΑ               |

| Input logic low current $(V_{in} = 0 \text{ V, resistors set to pull-up}^{\dagger})$    |        | –75 μΑ              |

| Input logic low current $(V_{in} = 0 \text{ V, resistors set to pull-down}^{\dagger})$  | _      | -10 μA <sup>‡</sup> |

<sup>&</sup>lt;sup>†</sup> The PCI-DIO-96 bias resistors are always set to pull-up. On the PXI-6508 and PCI-6503, use jumper W1 to select pull-up or pull-down.

# **Output Signals**

Pin 49 (at +5 V) ......1.0 A max

| Level                                                    | Min   | Max   |

|----------------------------------------------------------|-------|-------|

| Output logic high voltage ( $I_{ol} = -2.5 \text{ mA}$ ) | 3.0 V | 5.0 V |

| Output logic high voltage ( $I_{oh} = -4 \text{ mA}$ )   | 2.7 V | 5.0 V |

| Output logic low voltage ( $I_{ol} = 2.5 \text{ mA}$ )   | 0 V   | 0.4 V |

| Output logic low voltage ( $I_{ol} = 4 \text{ mA}$ )     | 0 V   | 0.5 V |

Output current......2.5 mA typ

**Caution** Drawing more than the typical 2.5 mA current ( $<2~k\Omega$  load at 5 V output) can cause serious damage to the device 82C55 PPI. The 82C55 PPI is intended for use as a logic device, and should not be used as current driver for LEDs, SSRs, mechanical relays, and so on, which can have low impedance loads and/or require high current drive. If you require higher current drive, consider using the NI PCI/PXI-6509 5V/TTL 96-line Industrial DIO board with 24 mA current driver, using an NI PCI/PXI-651x high-current drive Industrial DIO board, or using external circuitry such as Darlington Arrays to increase the current drive of digital output lines. For more information about the breakdown levels of your device and for a link to the 82C55 data sheets, refer to ni.com/info and enter the info code 82c55.

<sup>‡</sup> Exception: Lines PC3 and PC0 are 20 μA.

#### **Transfer Rates**

Max with NI-DAQ software ...... 50 kbytes/s

Constant sustainable rate (typ)...... 1 to 10 kbytes/s

Transfer rates are a function of the speed with which your program reads data from or writes data to the board, and therefore vary with your system, software, and application. The following primary factors control your DIO board transfer rates:

- Computer system performance

- Programming environment (register-level programming or NI-DAQ)

- Programming language and code efficiency

- Execution mode (foreground or background, with background execution typically using interrupts)

- Other operations in progress

- Application

For example, you can obtain higher transfer rates in a handshaking or data-transfer application, requiring an average rate, than in a pattern generation, data acquisition, or waveform generation application, requiring a constant sustainable rate.

The maximum rate shown was obtained using a 233 MHz Pentium computer running Traditional NI-DAQ (Legacy) and LabWindows/CVI software, with interrupt-based execution, and with no other high-speed operations in progress.

## **Bus Interface**

## **Power Requirement**

Power available at I/O connector ...... +4.65 to +5.25 V fused at 1 A

# **Physical**

| Dimensions                    |                                                  |

|-------------------------------|--------------------------------------------------|

| PCI-DIO-9613.7 ×              | $10.7 \text{ cm} (5.4 \times 4.2 \text{ in.})$   |

| PXI-650817.5 ×                | $(10.7 \text{ cm} (6.9 \times 4.2 \text{ in.}))$ |

| PCI-650312.2 ×                | $(9.5 \text{ cm} (4.8 \times 3.7 \text{ in.}))$  |

| Weight                        |                                                  |

| PCI-DIO-96101 g               | (3.6 oz)                                         |

| PXI-6508148 g                 | (5.2 oz)                                         |

| PCI-650355 g (                | 1.9 oz)                                          |

| I/O connector                 |                                                  |

| PCI-DIO-96 and PXI-6508100-p. | in female 0.050 series                           |

| D-type                        | e                                                |

| PCI-650350-pir                | n male ribbon-cable                              |

| conne                         | ctor                                             |

# **Environment**

If you need to clean the module, use a soft, non-metallic brush.

Operating temperature ......0 to 55 °C

Storage temperature ......20 to 70 °C

Relative humidity .....5% to 90%, noncondensing

Maximum altitude......2,000 meters

Pollution Degree ......2

Indoor use only.

#### **Shock and Vibration**

| Functional shock (PXI-6508)     | MIL-T-28800 E Class 3              |  |  |  |  |

|---------------------------------|------------------------------------|--|--|--|--|

|                                 | (per Section 4.5.5.4.1); half-sine |  |  |  |  |

|                                 | shock pulse, 11 ms duration,       |  |  |  |  |

|                                 | 30 g peak, 30 shocks per face      |  |  |  |  |

| Operational random vibration    |                                    |  |  |  |  |

| (PXI-6508)                      | 5 to 500 Hz, 0.31 grms, 3 axes     |  |  |  |  |

| Nonoperational random vibration |                                    |  |  |  |  |

(PXI-6508) ....... 5 to 500 Hz, 2.5 grms, 3 axes

**Note** Random vibration profiles were developed in accordance with MIL-T-28800E and MIL-STD-810E Method 514. Test levels exceed those recommended in MIL-STD-810E for Category 1 (Basic Transportation, Figures 514.4-1 through 514.4-3).

# Safety

The PCI-DIO-96/PXI-6508/PCI-6503 meets the requirements of the following standards of safety for electrical equipment for measurement, control, and laboratory use:

- IEC 61010-1, EN 61010-1

- UL 61010-1, CSA 61010-1

**Note** For UL and other safety certifications, refer to the product label or the *Online Product Certification* section.

## **Electromagnetic Compatibility**

This product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:

- EN 61326 (IEC 61326): Class A emissions; Basic immunity

- EN 55011 (CISPR 11): Group 1, Class A emissions

- AS/NZS CISPR 11: Group 1, Class A emissions

- FCC 47 CFR Part 15B: Class A emissions

- ICES-001: Class A emissions

**Note** For the standards applied to assess the EMC of this product, refer to the *Online Product Certification* section.

**Note** For EMC compliance, operate this device with shielded cabling.

# CE Compliance $\subset \in$

This product meets the essential requirements of applicable European Directives as follows:

- 2006/95/EC; Low-Voltage Directive (safety)

- 2004/108/EC; Electromagnetic Compatibility Directive (EMC)

#### Online Product Certification

Refer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for this product, visit ni.com/certification, search by model number or product line, and click the appropriate link in the Certification column.

# **Environmental Management**

NI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.

For additional environmental information, refer to the *NI and the Environment* Web page at ni.com/environment. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.

# Waste Electrical and Electronic Equipment (WEEE)

**EU Customers** At the end of their life cycle, all products *must* be sent to a WEEE recycling center. For more information about WEEE recycling centers and National Instruments WEEE initiatives, visit ni.com/environment/weee.htm.

#### 电子信息产品污染控制管理办法 (中国 RoHS)

中国客户 National Instruments 符合中国电子信息产品中限制使用某些有害物质指令 (RoHS)。 关于 National Instruments 中国 RoHS 合规性信息,请登录 ni.com/environment/rohs\_china。 (For information about China RoHS compliance, go to ni.com/environment/rohs\_china.)

# **Register-Level Programming**

This appendix describes in detail the address and function of each PCI-DIO-96, PXI-6508, and PCI-6503 register, contains instructions on how to operate DIO board circuitry, and provides examples of the programming steps necessary to execute an operation.

**Note** Current revisions of the NI PCI-DIO-96 and PXI-6508 no longer support the OKI 82C53 programmable interval timer. If you are using a PCI-DIO-96 revision G or earlier or PXI-6508 revision D or earlier, refer to the information in this appendix.

**Note** If you plan to use a programming software package such as LabVIEW, LabWindows/CVI, NI-DAQmx, or Traditional NI-DAQ (Legacy) with your DIO board, you need not read this appendix.

While it is possible to program your DAQ device at the register level, National Instruments strongly recommends using NI-DAQmx, Traditional NI-DAQ (Legacy), or driver software and application development software such as LabVIEW, Measurement Studio for Visual Studio .NET, or LabWindows/CVI to program your NI PCI-DIO-96, PXI-6508, and PCI-6503 device for improved productivity. NI-DAQmx and Traditional NI-DAQ (Legacy) software provides easier programming with the same flexibility as register-level programming.

NI-DAQmx and Traditional NI-DAQ (Legacy) driver software will not work for your programming needs in some cases, however. For example, if you are programming your 82C53 for hardware-timed interrupts or you are programming your DAQ device in an OS that is unsupported in NI-DAQmx or Traditional NI-DAQ (Legacy), NI-DAQmx Base software could be used as an alternative. If your OS is also unsupported in NI-DAQmx Base, you would then need to program your device using this appendix.

The NI Measurement Hardware Driver Development Kit (MHDDK) provides register-level programming examples and a bus interface for many operating systems. The MHDDK is a good starting point for developing a custom driver. You will also need the register map in this appendix. Note that some advanced functionalities such as interrupts are only covered in the examples in this appendix and not in the MHDDK examples. To access this document, go to ni.com/info and enter the info code mhddk.

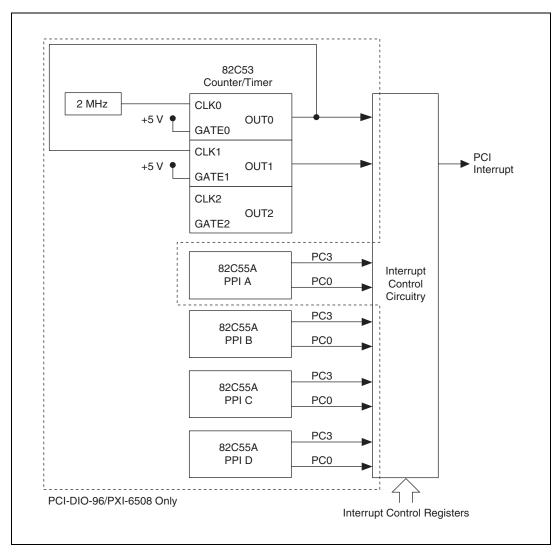

# 82C53 Programmable Interval Timer (PCI-DIO-96, PXI-6508 Only)

The PCI-DIO-96 and PXI-6508 contain an 82C53 programmable interval timer for use by register-level programmers only. The 82C53 programmable interval timer can generate timed interrupt requests to your computer. The 82C53 has three 16-bit counters, which can each be used in one of six different modes. The PCI-DIO-96 and PXI-6508 can use two of the counters to generate interrupt requests; the third counter is not used and is not accessible. Refer to the *Programming Considerations for the 82C53* section for more detailed information.

# **Interrupt Control Circuitry**

Two software-controlled registers determine which devices, if any, generate interrupts. Each of the 82C55A devices has two interrupt lines, PC3 and PC0, connected to the interrupt circuitry. On the PCI-DIO-96 and PXI-6508, the 82C53 device has two of its three counter outputs connected to the interrupt circuitry. Any of these 10 signals can interrupt the computer if the interrupt circuitry is enabled and the corresponding enable bit is set. Refer to the *Programming Considerations for the 82C53* section for more information. Normally, the handshaking circuitry controls PC3 and PC0 of the 82C55A devices; however, you can configure either of these two lines for input and then use them as external interrupts. An interrupt occurs on the signal line low-to-high transition.

Refer to the *Programming Considerations for the 82C53* section for more detailed information concerning interrupts.

The block diagram in Figure B-1 illustrates the interrupt control circuitry.

Figure B-1. Interrupt Control Circuitry Block Diagram

# **Register Map and Description**

This section describes in detail the address and function of each PCI-DIO-96, PXI-6508, and PCI-6503 register.

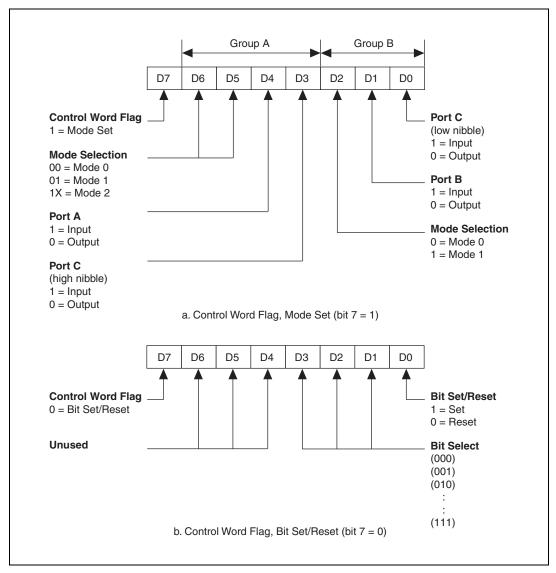

#### Introduction

The three 8-bit ports of the 82C55A are divided into two groups of 12 signals: group A and group B. One 8-bit control word selects the mode of operation for each group. The group A control bits configure port A (A<7..0>) and the upper 4 bits (nibble) of port C (C<7..4>). The group B control bits configure port B (B<7..0>) and the lower nibble of port C (C<3..0>). These configuration bits are defined in the *Register Description for the 82C55A* section. When differentiation is required between the four 82C55A PPI devices on the PCI-DIO-96 and PXI-6508, they are referenced as PPI A, PPI B, PPI C, and PPI D.

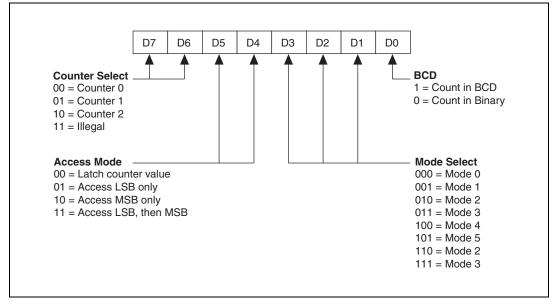

On the PCI-DIO-96 and PXI-6508, the three 16-bit counters of the 82C53 are accessed through individual data ports and controlled by one 8-bit control word. The control word selects how the counter data ports are accessed and what mode the counter uses. The *Register Description for the 82C53 (PCI-DIO-96, PXI-6508 Only)* section contains definitions for these configuration bits.

In addition to the 82C55A and 82C53 devices, there are two registers that select which onboard signals are capable of generating interrupts. There are two interrupt signals from each of the 82C55A devices and two interrupt signals from the 82C53 device. Individual enable bits select which of these 10 signals can generate interrupts. Also, a master enable signal determines whether the board can actually send a request to the computer. The *Register Description for the Interrupt Control Registers* section contains definitions for the configuration bits for these registers.

# **Register Map**

Table B-1 lists the address map for your DIO board. The PCI-DIO-96 and PXI-6508 use all of the registers. The PCI-6503 uses a subset of the registers, as indicated in the table.

Table B-1. Register Address Map

Appendix B

| Register Name                   | Offset Address<br>(Hex) | Size  | Туре           | Present on the<br>PCI-6503 |

|---------------------------------|-------------------------|-------|----------------|----------------------------|

| 82C55A Register Group           |                         |       |                |                            |

| PPI A                           |                         |       |                |                            |

| PORTA Register                  | 00                      | 8-bit | Read-and-write | Yes                        |

| PORTB Register                  | 01                      | 8-bit | Read-and-write | Yes                        |

| PORTC Register                  | 02                      | 8-bit | Read-and-write | Yes                        |

| Configuration Register          | 03                      | 8-bit | Write-only     | Yes                        |

| 82C55A Register Group (Contin   | ued)                    |       |                |                            |

| РРІ В                           |                         |       |                |                            |

| PORTA Register                  | 04                      | 8-bit | Read-and-write | No                         |

| PORTB Register                  | 05                      | 8-bit | Read-and-write | No                         |

| PORTC Register                  | 06                      | 8-bit | Read-and-write | No                         |