#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

## **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

PXI-1042

## **INSTALLATION GUIDE**

# 8-Slot PXI Backplane

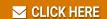

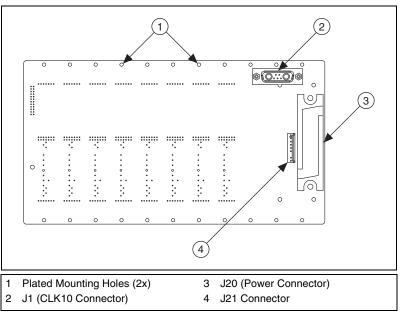

This guide describes installation requirements for the 8-slot PXI backplane, shown in Figure 1.

Figure 1. 8-Slot PXI Backplane

# **Description**

The 8-slot PXI backplane contains one PXI controller slot and 7 PXI peripheral slots. It does not include a power supply or cooling solution. You must implement these features when installing the backplane into your system.

# **Mechanical Requirements**

## Mounting

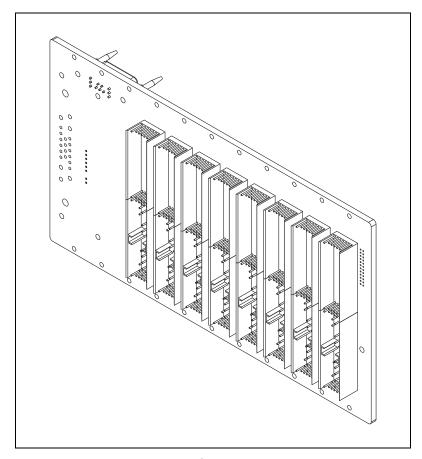

Figure 2 shows the backplane dimensions. There are 22 holes available for mounting with M2.5 hardware.

The use of all mounting holes is recommended for proper backplane support.

There are two mounting holes on top of the 8-slot PXI backplane that have plated annular pads on the front and back of the backplane. These mounting holes may be used to connect the backplane ground to the chassis in which the backplane is mounted. If you do not desire to connect backplane ground to the chassis, use insulated washers at these mounting holes. Refer to Figure 4 for the position of the mounting holes.

## Cooling

**Note** National Instruments is not responsible for damage to the backplane if inadequate cooling is used.

You should mount a fan below the backplane. Airflow should be from the bottom to the top of the PXI modules. You must determine the airflow requirements for your system based on the PXI Hardware Specification.

# **Handling**

**Cautions** Be careful to avoid bending or otherwise damaging the pins on the backplane connectors. Bent pins may cause functional failures or damage when the backplane is powered.

To protect both yourself and the backplane from electrical hazards, leave the chassis powered off until you finish installing the PXI controller and modules.

**Caution** Electrostatic discharge can damage your equipment. To avoid such damage, discharge the static built up on your body by touching a grounded metal object before handling the PXI equipment. Then touch the antistatic plastic package containing the backplane to a metal part of your PXI chassis before removing the backplane from the packaging.

#### **Dimensions**

Figure 2. Dimensions

# **Electrical Requirements**

#### **PXI Connectors**

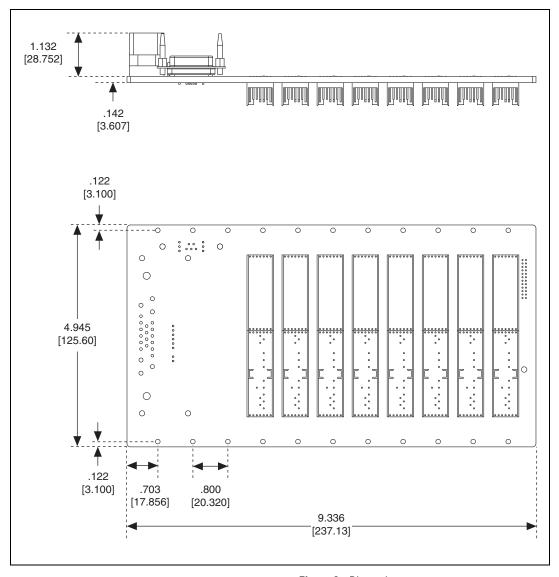

The PXI connectors (J11-J18, J2-J9) have pin descriptions defined in the *PXI hardware Specification*. The connectors are shown in Figure 3.

Figure 3. PXI Connectors

## **System Reference Clock**

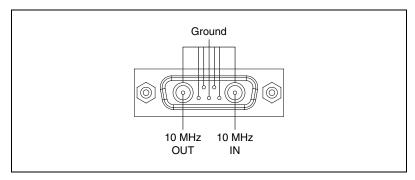

The 8-Slot Backplane supplies the PXI 10 MHz system clock signal (PXI\_CLK10) independently to each peripheral slot. An independent buffer (having a source impedance matched to the backplane and a skew of less than 250 ps between slots) drives the clock signal to each peripheral slot. You can use this common reference clock signal to synchronize multiple modules in a measurement or control system. You can drive PXI\_CLK10 from an external source through the PXI\_CLK10\_IN pin on the P2 connector of the Star Trigger Slot or 10 MHz IN pin on the J1 connector. Refer to the *PXI Specification* for the Pinout for the Star Trigger Slot. Sourcing an external clock on either of these pins automatically replaces the backplane's 10 MHz source.

Figure 4. Backplane Power and CLK10 Connectors

#### **Power**

Please refer to the *PXI Hardware Specification* for power requirements and to the specifications of the chosen power supply to determine the minimum load required.

#### **Connector J20**

Connector J20 is the power supply connector for the 8-slot backplane. The location of the J20 connector is shown in Figure 4. Refer to Table 1 for the pin descriptions. The mating connector for J20 is manufactured by Tyco Electronics, and can be ordered with the part number 1648115-1.

**Note** The system slot (slot 1) receives +12 V power from pin 17 of J20. If this pin is not connected to +12 V the system controller will not function properly.

Table 1. Connector J20 Pin Descriptions

| Connector   | Pin | Signal            | Description                           | Required<br>for Basic<br>Power-up |

|-------------|-----|-------------------|---------------------------------------|-----------------------------------|

|             | 1   | +3.3 V            | Backplane +3.3 V power plane.         | Yes                               |

|             | 2   | GND               | Backplane ground plane.               | Yes                               |

|             | 3   | +3.3 V            | Backplane +3.3 V power plane.         | Yes                               |

|             | 4   | LED2              | Connects to pin 8 of J21.             | No                                |

|             | 5   | INHIBIT           | Connects to pin 7 of J21.             | No                                |

|             | 6   | LED1              | Connects to pin 5 of J21.             | No                                |

|             | 7   | SMB_SDA           | Connects to pin C19 on J2 (slot 1).   | No                                |

|             | 8   | SMB_ALERT#        | Connects to pin E19 on J2 (slot 1).   | No                                |

| 3 - 4 5 - 6 | 9   | SMB_SCL           | Connects to pin D19 on J2 (slot 1).   | No                                |

|             | 10  | THERM1 (optional) | Connects to pin 2 of J21.             | No                                |

| 8           | 11  | THERM2 (optional) | Connects to pin 1 of J21.             | No                                |

| 11          | 12  | GND               | Backplane ground plane.               | Yes                               |

|             | 13  | GND               | Backplane ground plane.               | Yes                               |

|             | 14  | -12 V             | Backplane –12 V power plane.          | Yes                               |

|             | 15  | I2C_CLK           | Connects through R34 to pin A2 of J9. | No                                |

|             | 16  | I2C_DAT           | Connects through R33 to pin B2 of J9. | No                                |

|             | 17  | +12 V_FAN         | Separate +12 V for slot 1.            | Yes                               |

|             | 18  | GND               | Backplane ground plane.               | Yes                               |

|             | 19  | +12 V             | Backplane +12 V power plane.          | Yes                               |

|             | 20  | GND               | Backplane ground plane.               | Yes                               |

|             | 21  | +5 V              | Backplane +5 V power plane.           | Yes                               |

|             | 22  | GND               | Backplane ground plane.               | Yes                               |

### **Connector J1**

Connector J1 is for interfacing with the backplane's PXI\_CLK10 circuitry. The location of the J1 connector is shown in Figure 4. The mating connector for J1 is manufactured by Positronic and can be ordered with the part number CBD7W2M2000Z-759.1.

Figure 5. J1 Connector

#### **Connector J21**

Connector J21 may be used in conjunction with J20 for interfacing with an inhibit switch, LED, and thermistor. It is not necessary to connect to J21 for basic power-up of the backplane. Refer to Table 2 for the pin descriptions. The mating connector for pins 1–6 of J21 is manufactured by Molex and can be ordered with the part number 22-01-2067.

Table 2. Connector J21 Pin Descriptions

| Connector | Pin | Signal   | Description                              |

|-----------|-----|----------|------------------------------------------|

| 8         | 1   | THERM2   | Connects to pin 11 of J20                |

|           | 2   | THERM1   | Connects to pin 10 of J20                |

|           | 3   | (No Pin) | _                                        |

|           | 4   | NC       | Not connected.                           |

|           | 5   | LED1     | Connects to pin 6 of J20.                |

|           | 6   | +5V      | Connects to backplane's +5V power plane. |

|           | 7   | INH      | Connects to pin 5 of J20.                |

|           | 8   | LED2     | Connects to pin 4 of J20.                |

|           | 9   | GND      | Connects to backplane's ground plane.    |

# Backplane

| Size                          | three system expansion slots) and seven peripheral slots. Compliant with IEEE 1101.10 mechanical packaging. PXI Specification Revision 2.0 compliant. Accepts both PXI and CompactPCI (PICMG 2.0 R 3.0) 3U modules. |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Backplane bare-board material | UL 94 V-0 Recognized                                                                                                                                                                                                |

| Backplane connectors          | Conforms to IEC 917 and IEC 1076-4-101, and are UL 94 V-0 rated                                                                                                                                                     |

| RoHS                          | 8-slot PXI backplane is<br>RoHS-compliant                                                                                                                                                                           |

| 10 MHz System Reference       | Clock (PXI_CLK10)                                                                                                                                                                                                   |

| Maximum clock skew            | ·                                                                                                                                                                                                                   |

| between slots                 | 250 ps                                                                                                                                                                                                              |

| Built-in 10 MHz clock         |                                                                                                                                                                                                                     |

| Accuracy                      | +25 nnm (quaranteed ever the                                                                                                                                                                                        |

| Accuracy                      | operating temperature range)                                                                                                                                                                                        |

| Maximum jitter                |                                                                                                                                                                                                                     |

| External clock sources        |                                                                                                                                                                                                                     |

|                               | Connector J1 on rear of backplane<br>(ground referenced) or Slot 2 J2<br>(pin D17)                                                                                                                                  |

| Input frequency               | 10 MHz ±100 ppm or better                                                                                                                                                                                           |

| Input amplitude               |                                                                                                                                                                                                                     |

| • •                           | 200 mV <sub>pp</sub> to 5 V <sub>pp</sub> , 10 MHz<br>squarewave or sinewave                                                                                                                                        |

| Slot 2                        | 5 V or 3.3 V, 10 MHz TTL signal                                                                                                                                                                                     |

| Input impedance               |                                                                                                                                                                                                                     |

| Maximum jitter introduced     | •                                                                                                                                                                                                                   |

| by backplane circuitry        | 1 ps RMS in 10 Hz to 1 MHz range                                                                                                                                                                                    |

#### External clock output

| Connector        | . Connector J1 on rear of backplane           |

|------------------|-----------------------------------------------|

|                  | (ground-referenced)                           |

| Output amplitude | . 1 $V_{pp}$ ±20% squarewave into 50 $\Omega$ |

|                  | 2 V <sub>pp</sub> into open circuit           |

| Output impedance | $.50 \Omega \pm 5 \Omega$                     |

9

| National Instruments, NI, ni.com, and LabVIEW are trademarks of National Instruments Corporation. Refer to the Terms of Use section on ni.com/legal for more information about National Instruments trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies. For patents covering National Instruments products, refer to the appropriate location: Help»Patents in your software, the patents.txt file on your CD, or ni.com/patents. |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| © 2007 National Instruments Corporation. All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |