#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### SELL YOUR SURPLUS

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs. Ally Sell For Cash Ally Get Credit Ally Receive a Trade-In Deal

**OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

# APEX WAVES

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

$\bigtriangledown$

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote CLICK HERE PCIe-6535B

# SPECIFICATIONS NI PXIe/PCIe-6535/6536/6537 and NI PCIe-6535B/6536B/6537B

10/25/50 MHz Digital I/O Device

このドキュメントには、日本語ページも含まれています。

This document provides specifications for NI PXIe/PCIe-6535/6536/6537 (NI 6535/6536/6537) and NI PCIe-6535B/6536B/6537B (NI 6535B/6536B/6537B) digital I/O devices.

Specifications are subject to change without notice. For the most recent specifications visit ni.com/manuals.

**Caution** All values were obtained using a 1 m cable (SHC68-C68-D4 recommended). Performance specifications are not guaranteed when using longer cables.

*Warranted* specifications are warranted not to exceed these values within certain operating conditions and include the effects of temperature and uncertainty unless otherwise noted.

*Typical* specifications are unwarranted values that are representative of a majority  $(3\sigma)$  of units within certain operating conditions and include the effects of temperature and uncertainty unless otherwise noted.

*Nominal* specifications are unwarranted values that are relevant to the use of the product and convey the expected performance of the product.

All specifications are *Typical* unless otherwise noted. These specifications are valid within the operating temperature range. All warranted specifications will be specifically denoted as *Warranted* in the comment section of the specification.

## Contents

| Channel Specifications                                   | 2  |

|----------------------------------------------------------|----|

| Generation Channels (Data and PFI <05> Channels)         | 3  |

| Acquisition Channels (Data and PFI <05> Channels)        | 4  |

| Timing Specifications                                    | 5  |

| Sample Clock                                             |    |

| Pattern Generation Timing (Data and PFI 4 Channels)      | 7  |

| Pattern Acquisition Timing (Data and PFI 5 Channels)     | 9  |

| Handshaking                                              | 10 |

| Change Detection                                         | 11 |

| Waveform Specifications                                  | 11 |

| Memory                                                   |    |

| Triggers                                                 | 12 |

| Events                                                   | 16 |

| Nonvolatile Storage                                      | 17 |

| Power                                                    | 17 |

| Physical Specifications                                  | 18 |

| Software                                                 |    |

| Environment                                              | 19 |

| Safety, Electromagnetic Compatibility, and CE Compliance | 20 |

| Worldwide Support and Services                           |    |

# **Channel Specifications**

| Specification                                                        | Value       | Comments                                                                                                               |

|----------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------|

| Number of data channels                                              | 32          | —                                                                                                                      |

| Direction<br>control of data<br>channels                             | Per channel | _                                                                                                                      |

| Number of<br>Programmable<br>Function<br>Interface (PFI)<br>channels | 6           | Refer to the<br><i>Waveform</i><br><i>Specifications</i><br>section for more<br>information about<br>the PFI channels. |

| Direction<br>control of<br>PFI channels                              | Per channel | _                                                                                                                      |

| Specification                                           | Va                                                                                                                                                                                                | Value         |                                                                                                 |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------|--|

| Number of                                               | PXI Express                                                                                                                                                                                       | PCI Express   | PXI_TRIG7 is not                                                                                |  |

| RTSI/PXI<br>trigger channels                            | 10 (PXI_TRIG<07>,<br>PXIe_DSTARB,<br>PXIe_DSTARC)                                                                                                                                                 | 8 (RTSI <07>) | supported as input<br>trigger.                                                                  |  |

| Direction<br>control of<br>RTSI/PXI<br>trigger channels | RTSI <07>/PXI_TRIG<07>: Bidirectional; per channel<br>PXIe_DSTARB: Unidirectional input (PXI Express only)<br>PXIe_DSTARC: Unidirectional output (PXI Express only)                               |               |                                                                                                 |  |

| Number of<br>Sample clock<br>terminals                  | 3 bidirectional clock terminals (PFI 4, PFI 5, RTSI 7)<br>1 exported clock terminal (PXIe_DSTARC)<br>(PXI Express only)<br>2 clock source terminals (PXIe_DSTARA, PXI_STAR)<br>(PXI Express only) |               | Refer to <i>Timing</i><br><i>Specifications</i> for<br>more information<br>about clock sources. |  |

## Generation Channels (Data and PFI <0..5> Channels)

| Specification                                       |                                    | Value                             |            |            |                               |

|-----------------------------------------------------|------------------------------------|-----------------------------------|------------|------------|-------------------------------|

| Generation<br>voltage<br>families                   | 2.5 V, 3.3 V (5                    | 2.5 V, 3.3 V (5 V TTL compatible) |            |            | _                             |

| Generation<br>signal type                           | Single-ended                       | Single-ended                      |            |            | _                             |

| Generation                                          | Low Volta                          | ge Levels                         | High Volta | ige Levels | Warranted.                    |

| voltage levels                                      | Typical                            | Maximum                           | Minimum    | Typical    | Into high<br>impedance        |

| 2.5 V                                               | 0.0 V                              | 0.1 V                             | 2.4 V      | 2.5 V      | load.                         |

| 3.3 V                                               | 0.0 V                              | 0.1 V                             | 3.2 V      | 3.3 V      | Production<br>tested for data |

| 5.0 V                                               | 0.0 V                              | 0.1 V                             | 3.2 V      | 3.3 V      | channels.                     |

| Output<br>impedance                                 | 50 $\Omega$ , nominal              | 50 $\Omega$ , nominal             |            |            |                               |

| Maximum DC<br>drive strength                        | ±16 mA at 2.5 V<br>±32 mA at 3.3 V |                                   |            |            | _                             |

| Data channel<br>driver<br>enable/disable<br>control | Per channel                        | Per channel                       |            |            |                               |

| Specification             | Value                                                                           | Comments                                                                           |

|---------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Channel<br>power-up state | Software programmable (Tristate, 0, or 1 at 2.5 V or 3.3 V)                     | Channel data is<br>typically valid<br>1.5 s after the<br>power-up state<br>is set. |

| Output<br>protection      | The device can indefinitely sustain a short to any voltage between 0 V and 5 V. |                                                                                    |

## Acquisition Channels (Data and PFI <0..5> Channels)

| Specification                      | Va                                    | ue                                 | Comments                                                                                           |

|------------------------------------|---------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------|

| Acquisition<br>voltage<br>families | 2.5 V, 3.3 V (5 V TTL compatible)     |                                    | —                                                                                                  |

| Acquisition<br>voltage levels      | Low Voltage Thresholds<br>Maximum     | High Voltage Thresholds<br>Minimum | Warranted.<br>Production                                                                           |

| 2.5 V                              | 0.75 V                                | 1.75 V                             | tested for data channels.                                                                          |

| 3.3 V                              | 1.00 V                                | 2.30 V                             |                                                                                                    |

| 5.0 V                              | 1.00 V                                | 2.30 V                             |                                                                                                    |

| Input<br>impedance                 | High-impedance (50 k $\Omega$ to grou | nd)                                | —                                                                                                  |

| Input<br>protection                | -1 V to +6 V                          |                                    | Diode clamps<br>in the design<br>may provide<br>additional<br>protection<br>outside this<br>range. |

## Sample Clock

| Specification                                                | V                                                                                                                                                                                                                                                                                             | /alue                                         | Comments                                                                                                                                                                                          |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sample clock<br>sources                                      | <ol> <li>On Board Clock (Sample Clock Timebase with<br/>divider)</li> <li>PFI &lt;45&gt;</li> <li>PXI_TRIG7 (PXI backplane)<sup>†</sup><br/>RTSI 7 (RTSI bus)<sup>1‡</sup></li> <li>PXI_STAR (PXI backplane)<sup>†</sup></li> <li>PXIe_DSTARA (PXI backplane)<sup>†</sup></li> </ol>          |                                               | Refer to the <i>Clocking</i><br>diagram in the<br><i>NI 6535/6536/6537 and</i><br><i>NI 6535B/6536B/6537B</i><br><i>Help</i> for an illustration of<br>the various clock and<br>timebase sources. |

| Sample clock<br>timebase<br>sources                          | <ol> <li>PARDSTARGY (PAP obckplane)</li> <li>200 MHz Timebase (internal oscillator)</li> <li>PFI &lt;05&gt;</li> <li>PXI_TRIG&lt;06&gt; (PXI backplane)<sup>†</sup><br/>RTSI &lt;07&gt; (RTSI bus)<sup>‡</sup></li> <li>PXIe DSTARB (PXI backplane)<sup>†</sup></li> </ol>                    |                                               |                                                                                                                                                                                                   |

| On Board<br>Clock<br>frequency range                         | <b>NI 6535/6535B</b> : 48 Hz to 10 MHz<br>Configurable to 200 MHz/N; $20 \le N \le 4,194,307$<br><b>NI 6536/6536B</b> : 48 Hz to 25 MHz<br>Configurable to 200 MHz/N; $8 \le N \le 4,194,307$<br><b>NI 6537/6537B</b> : 48 Hz to 50 MHz<br>Configurable to 200 MHz/N; $4 \le N \le 4,194,307$ |                                               | _                                                                                                                                                                                                 |

| Imported<br>Sample clock                                     | PFI <45><br>PXIe_DSTARA <sup>†</sup>                                                                                                                                                                                                                                                          | PXI_TRIG7 <sup>†</sup><br>RTSI 7 <sup>‡</sup> | _                                                                                                                                                                                                 |

| frequency range                                              | NI 6535/6535B:         NI 6535/6535B:           0 Hz to 10 MHz         0 Hz to 10 MHz           NI 6536/6536B:         NI 6536/6536B and           0 Hz to 25 MHz         NI 6537/6537B:           NI 6537/6537B:         0 Hz to 25 MHz           0 Hz to 50 MHz         0 Hz to 25 MHz      |                                               |                                                                                                                                                                                                   |

| <sup>†</sup> PXI Express onl<br><sup>‡</sup> PCI Express onl | -                                                                                                                                                                                                                                                                                             |                                               |                                                                                                                                                                                                   |

| Specification                                                |                                                                                                                     | v      | /alue                                                 |                                               | Comments                                        |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------|-----------------------------------------------|-------------------------------------------------|

| Minimum<br>detectable                                        | PFI <45>                                                                                                            | PXIe_D | STARA†                                                | PXI_TRIG7 <sup>†</sup><br>RTSI 7 <sup>‡</sup> | Positive and negative pulse width at voltage    |

| Sample clock<br>pulse width                                  | 8 ns                                                                                                                | 15 ns  | /6535B<br>/6536B:<br>/6537B:                          | 15 ns                                         | thresholds.                                     |

| Imported<br>timebase clock                                   | PFI <0<br>PXIe_DST/                                                                                                 |        | Р                                                     | XI_TRIG7 <sup>†</sup><br>RTSI 7 <sup>‡</sup>  | _                                               |

| frequency range                                              | <b>NI 6535/6535</b><br>0 Hz to 10 MH                                                                                |        | <b>NI 6535</b><br>0 Hz to                             | <b>/6535B</b> :<br>10 MHz                     |                                                 |

|                                                              | <b>NI 6536/6536</b><br>0 Hz to 25 MH                                                                                |        | NI 6536/6536B and<br>NI 6537/6537B:<br>0 Hz to 25 MHz |                                               |                                                 |

|                                                              | <b>NI 6537/6537</b><br>0 Hz to 50 MH                                                                                |        |                                                       |                                               |                                                 |

| Minimum<br>detectable                                        | PFI <4<br>PXIe_DST/                                                                                                 |        | Р                                                     | XI_TRIG7 <sup>†</sup><br>RTSI 7 <sup>‡</sup>  | Positive and negative<br>pulse width at voltage |

| imported<br>timebase clock<br>pulse width                    | 6.5 ns                                                                                                              |        | 15 ns                                                 |                                               | thresholds.                                     |

| Exported                                                     | Generat                                                                                                             | ion    | A                                                     | cquisition                                    | _                                               |

| Sample clock<br>destinations                                 | <ol> <li>PFI 4</li> <li>RTSI 7<sup>†</sup><br/>PXI_TRIG</li> <li>PXIe_DST</li> </ol>                                |        | PFI 5                                                 |                                               |                                                 |

| Exported<br>Sample clock<br>duty cycle                       | Internal Sample clock or divided-down timebase:<br>33% to 67%<br>Imported Sample clock: Limited by input duty cycle |        | Nominal.                                              |                                               |                                                 |

| <sup>†</sup> PXI Express onl<br><sup>‡</sup> PCI Express onl | <sup>†</sup> PXI Express only<br><sup>‡</sup> PCI Express only                                                      |        |                                                       |                                               |                                                 |

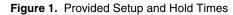

## Pattern Generation Timing (Data and PFI 4 Channels)

| Specification                                                                     | Va                                                                           | lue                                               | Comments                                                                                   |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------|

| Maximum data<br>channel toggle<br>rate                                            | NI 6535/6535B: 5.0 MHz<br>NI 6536/6536B: 12.5 MHz<br>NI 6537/6537B: 25.0 MHz |                                                   | _                                                                                          |

| Data position                                                                     | Data Channels                                                                | PFI Channels                                      | Relative to Sample                                                                         |

| modes                                                                             | Active edge, Inactive edge                                                   | Active edge                                       | clock; Active edge<br>may be rising or<br>falling.                                         |

| Minimum                                                                           | PXI Express                                                                  | PCI Express                                       | $t_P$ is the Sample clock                                                                  |

| provided hold<br>time with<br>respect to PFI 4<br>(t <sub>PH</sub> )              | 750 ps                                                                       | 1.1 ns                                            | interval; values<br>assume the sample is<br>generated and<br>acquired on the               |

| Minimum<br>provided setup<br>time with<br>respect to PFI 4<br>(t <sub>PSU</sub> ) | Sample clock interval<br>(t <sub>P</sub> ) - 5.35 ns                         | Sample clock interval<br>(t <sub>P</sub> ) - 5 ns | same clock edge;<br>includes maximum<br>channel-to-channel<br>skew; valid for all<br>data. |

Note Provided setup and hold times include channel-to-channel skew and jitter.

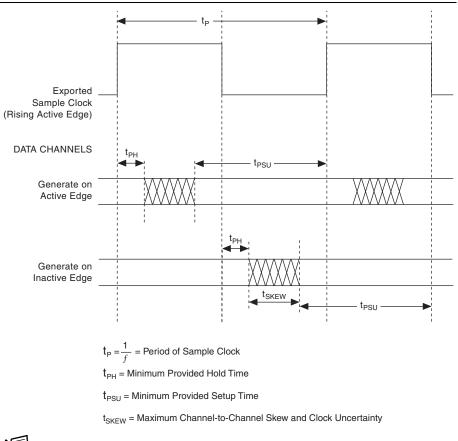

## Pattern Acquisition Timing (Data and PFI 5 Channels)

| Specification                                                               | Value                                                                                                          | Comments                                                                                                                                                            |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Setup time<br>with respect to<br>PFI 5 (t <sub>SU</sub> )                   | NI 6535/6536/6537 Rev C* or later<br>and NI 6535B/6536B/6537B: 2.8 ns<br>NI PCIe-6535/6536/6537 Rev B*: 2.0 ns | Includes maximum<br>data channel-to-<br>channel skew; valid for<br>data and all triggers                                                                            |

| Hold time with<br>respect to<br>PFI 5 (t <sub>H</sub> )                     | NI 6535/6536/6537 Rev C* or later           and NI 6535B/6536B/6537B: 1.5 ns                                   | except the Start trigger<br>when using the Sample<br>Clock sample timing<br>type.<br>* Refer to assembly<br>number sticker on<br>device for revision<br>information |

| Setup time of<br>triggers with<br>respect to<br>PFI 5 (t <sub>SCTSU</sub> ) | 15 ns                                                                                                          | Nominal.                                                                                                                                                            |

| Trigger delay<br>from PFI 5 to<br>trigger edge<br>(t <sub>PC</sub> )        | 9 ns                                                                                                           | Nominal.                                                                                                                                                            |

$t_{SU}$  = Setup Time with Respect to PFI 5

$t_{H}$  = Hold Time with Respect to PFI 5

$t_{P} = \frac{1}{f}$  = Sample Clock Period

$t_{SCPW}$  = Minimum Detectable Sample Clock Pulse Width

t<sub>PC</sub> = Trigger Delay from PFI 5 to Trigger Edge\*

t<sub>SCTSU</sub> = Setup Time of Trigger with Respect to PFI 5\*

\*Sample Clock Sample Timing Type only.

#### Handshaking

| Specification                                                                 | Value                                                                                           | Comments                      |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------|

| Asynchronous<br>handshaking<br>modes                                          | Handshake (8255) sample timing type                                                             | 8255 emulation<br>equivalent. |

| Synchronous<br>handshaking<br>modes                                           | <ol> <li>Burst sample timing type</li> <li>Pipelined Sample Clock sample timing type</li> </ol> | —                             |

| Control line<br>polarity                                                      | <ol> <li>Active high</li> <li>Active low</li> </ol>                                             | —                             |

| Programmable<br>delay<br>resolution for<br>Handshake<br>sample timing<br>type | 20 ns                                                                                           | —                             |

## **Change Detection**

| Specification                     | Value                                                                                                     | Comments               |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------|

| Change<br>detection<br>resolution | Sample clock period                                                                                       | —                      |

| Sources                           | P0.<07>, P1.<07>, P2.<07>, P3.<07>                                                                        | Per data               |

| Valid sample position             | <ol> <li>Active edge</li> <li>Inactive edge</li> </ol>                                                    | channel<br>selectable. |

| Valid changes                     | <ol> <li>Don't care</li> <li>Rising edge</li> <li>Falling edge</li> <li>Rising or falling edge</li> </ol> |                        |

# Waveform Specifications

#### Memory

| Specification                         | Value                                                                               | Comments                                                    |

|---------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Onboard<br>memory size                | 2,048 samples (S)                                                                   | First-in<br>first-out based,<br>regardless of<br>port size. |

| Transfer type                         | <ol> <li>DMA</li> <li>Programmed I/O (On Demand sample timing type only)</li> </ol> | —                                                           |

| Generation<br>waveform<br>quantum     | Waveform size must be an integer multiple of 1 S.                                   | —                                                           |

| Acquisition<br>minimum<br>buffer size | 2 S                                                                                 | _                                                           |

## Triggers

| Specification                       |                                                                                                                                                                                                                                                                                                                                                                                        | Value                                                                                                    |              | Comments                                   |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------|

| Supported<br>triggers<br>(by sample | Sample<br>Timing<br>Type                                                                                                                                                                                                                                                                                                                                                               | Acquisition                                                                                              | Generation   | Generation<br>operations do<br>not support |

| timing type)                        | Sample<br>Clock                                                                                                                                                                                                                                                                                                                                                                        | Start, Reference                                                                                         | Start        | pattern match triggers.                    |

|                                     | Pipelined<br>Sample<br>Clock                                                                                                                                                                                                                                                                                                                                                           | Pause, Start, Reference                                                                                  | Pause, Start |                                            |

|                                     | Burst<br>Handshake                                                                                                                                                                                                                                                                                                                                                                     | Pause (not including the pattern match type trigger)                                                     | Pause        |                                            |

|                                     | Handshake                                                                                                                                                                                                                                                                                                                                                                              | Handshake                                                                                                | Handshake    |                                            |

|                                     | Change<br>Detection                                                                                                                                                                                                                                                                                                                                                                    | Start                                                                                                    | N/A          |                                            |

| Sources                             | <ol> <li>PFI &lt;05&gt; (DDC connector)</li> <li>PXI_TRIG&lt;06&gt; (PXI backplane)<sup>†</sup><br/>RTSI &lt;07&gt; (RTSI bus)<sup>‡</sup></li> <li>PXIe_DSTARB (PXI backplane)<sup>†</sup></li> <li>Pattern match (Acquisition sessions only)</li> <li>Disabled (Do not wait for a trigger)</li> </ol>                                                                                |                                                                                                          | _            |                                            |

| Trigger detection                   | <ol> <li>Start Trigger (Edge detection: rising or falling;<br/>Pattern match: match or does not match)</li> <li>Pause Trigger (Level detection: high or low;<br/>Pattern match: match or does not match)</li> <li>Reference Trigger (Edge detection: rising or falling;<br/>Pattern match: match or does not match)</li> <li>Handshaking Trigger (Interlocked: high or low)</li> </ol> |                                                                                                          |              | _                                          |

| Destinations                        | 2. PXI_TRIG<br>RTSI <07                                                                                                                                                                                                                                                                                                                                                                | (DDC Connector)<br><07> (PXI backplane) <sup>†</sup><br>> (RTSI bus)<br>ARC (PXI backplane) <sup>†</sup> |              | —                                          |

| Specification                                                     |                                      | Value                                                                                                                                                                                                                                             |                                                                                      | Comments                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

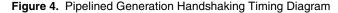

| Delay from<br>Pause trigger to                                    | Minimum                              | Generation<br>Maximum                                                                                                                                                                                                                             | Acquisition                                                                          | Use the Data<br>Active event                                                                                                                                                                                                                    |

| Paused state<br>(t <sub>P2S</sub> )                               | 6 Sample<br>clock cycles<br>+ 6.7 ns | NI PCle-6535/6536/6537:           7 Sample clock cycles +           15.4 ns           NI PXle-6535/6536/6537:           7 Sample clock cycles +           17 ns           NI 6535B/6536B/6537B:           7 Sample clock cycles +           65 ns | Synchronous<br>to the data                                                           | during<br>generation<br>operations to<br>determine on a<br>sample-by-<br>sample basis<br>when the NI<br>device has<br>entered the<br>Paused state.<br>Pause trigger<br>only supported<br>by Pipelined<br>Sample Clock<br>sample timing<br>type. |

| <sup>†</sup> PXI Express only                                     |                                      |                                                                                                                                                                                                                                                   |                                                                                      |                                                                                                                                                                                                                                                 |

| <sup>‡</sup> PCI Express only                                     |                                      |                                                                                                                                                                                                                                                   | 1                                                                                    | i                                                                                                                                                                                                                                               |

| Delay from<br>trigger to digital                                  |                                      | Generation                                                                                                                                                                                                                                        |                                                                                      | Nominal.                                                                                                                                                                                                                                        |

| data output ( $t_{T2D}$ )                                         | Minimum                              | Maximum                                                                                                                                                                                                                                           | Acquisition                                                                          |                                                                                                                                                                                                                                                 |

|                                                                   | 65 ns                                | NI 6535/6536/6537:<br>1 Sample clock cycle +<br>130 ns                                                                                                                                                                                            | N/A                                                                                  |                                                                                                                                                                                                                                                 |

|                                                                   |                                      | NI 6535B/6536B/6537B:<br>1 Sample clock cycle +<br>150 ns                                                                                                                                                                                         |                                                                                      |                                                                                                                                                                                                                                                 |

| Minimum<br>detectable<br>trigger pulse<br>width (t <sub>W</sub> ) | Type Tr<br>Sample Tim                | Clock Sample Timing<br>riggers and Pipelined<br>ing Type Generation Start<br>Trigger                                                                                                                                                              | Burst and<br>Pipelined<br>Sample<br>Timing<br>Type<br>Generation<br>Pause<br>Trigger | Nominal.<br>Maximum<br>required pulse<br>width to<br>guarantee<br>sampling by an<br>asynchronous<br>clock;                                                                                                                                      |

|                                                                   | 10 ns                                |                                                                                                                                                                                                                                                   | Sample clock<br>period + 4 ns                                                        | synchronous<br>triggers have<br>same setup<br>and hold<br>requirements as<br>data.                                                                                                                                                              |

| Specification                                                                                                          | Value                                                                                              | Comments                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum<br>required setup<br>and hold of<br>Sample Clock<br>sample timing<br>type triggers<br>with respect to<br>PFI 5 | Refer to the <i>Pattern Acquisition Timing (Data and PFI 5 Channels)</i> section of this document. | —                                                                                                                                            |

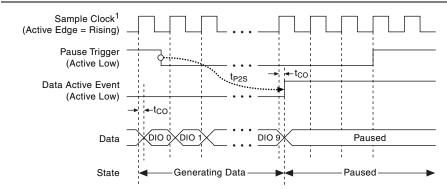

| Maximum<br>required delay<br>from data to<br>Handshake<br>trigger (t <sub>DT</sub> )                                   | 5 ns                                                                                               | Nominal.<br>Maximum<br>required time<br>between data<br>valid and the<br>Handshake<br>trigger;<br>Handshake<br>sample timing<br>type only.   |

| Maximum<br>required delay<br>from Handshake<br>trigger to data<br>(t <sub>TD</sub> )                                   | 50 ns                                                                                              | Nominal.<br>Maximum<br>required time<br>between the<br>Handshake<br>Trigger and data<br>invalid;<br>Handshake<br>sample timing<br>type only. |

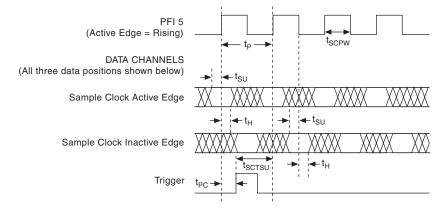

Figure 3. Pipelined Generation Timing Diagram

<sup>1</sup> Must be free-running.

<sup>2</sup> Generation pauses if the DAQmx Underflow property/attribute is set to Pause Until Data Available or Pause Trigger Received.

t<sub>w</sub> = Minimum detectable trigger pulse width.

t<sub>CO</sub> = Exported Sample clock offset.

$t_{T2D}$  = Delay from trigger to digital data out.

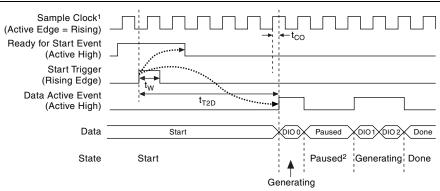

<sup>1</sup> Must be free-running.

t<sub>P2S</sub> = Pause trigger to Paused state.

t<sub>CO</sub> = Exported Sample clock offset.

$t_{\text{DT}}$  = Maximum required delay from data valid to trigger.  $t_{\text{TD}}$  = Maximum required delay from trigger to data invalid.

#### **Events**

| Specification              |                               | Value                                                                                                        |                                 | Comments |

|----------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------|----------|

| Supported events           | Sample<br>Timing Type         | Acquisition                                                                                                  | Generation                      | —        |

| (by sample<br>timing type) | Sample Clock                  | Ready for Start                                                                                              | Ready for Start,<br>Data Active |          |

|                            | Pipelined<br>Sample Clock     | Ready for<br>Transfer,<br>Ready for Start                                                                    | Ready for Start,<br>Data Active |          |

|                            | Burst<br>Handshake            | Ready for<br>Transfer                                                                                        | Ready for Transfer              |          |

|                            | Handshake                     | Handshake                                                                                                    | Handshake                       |          |

|                            | Change<br>Detection           | Change<br>Detection,<br>Ready for Start                                                                      | N/A                             |          |

| Destinations               | 2. PXI_TRIG<0.<br>RTSI <07> ( | DC Connector)<br>7> (PXI backplane) <sup>†</sup><br>RTSI bus) <sup>‡</sup><br>C (PXI backplane) <sup>†</sup> |                                 | —        |

| Specification                             | ,                               | Value                                                            | Comments                                                       |

|-------------------------------------------|---------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|

| Pulse width for                           | $Frequency \leq 10 \text{ MHz}$ | Frequency > 10 MHz <sup>∗</sup>                                  | Software                                                       |

| the exported<br>Change<br>Detection event | 50 ns                           | 15 ns                                                            | determined based<br>on Sample clock<br>frequency.              |

|                                           |                                 |                                                                  | * Frequency<br>>10 MHz does not<br>apply for<br>NI 6535/6535B. |

| <sup>†</sup> PXI Express onl              | ly                              |                                                                  |                                                                |

| ‡ PCI Express onl                         | у                               |                                                                  |                                                                |

| Delay from                                | Minimum                         | Maximum                                                          | Nominal.                                                       |

| Change Detect to event                    | 90 ns                           | <b>NI PCle-6535/6536/6537</b> :<br>1 Sample clock cycle + 100 ns | Delay from data at<br>the DDC connector<br>to the event        |

|                                           |                                 | <b>NI PXIe-6535/6536/6537</b> :<br>1 Sample clock cycle + 105 ns | generated on the DDC connector.                                |

|                                           |                                 | <b>NI 6535B/6536B/6537B</b> :<br>1 Sample clock cycle + 120 ns   |                                                                |

## Nonvolatile Storage

| Specification | Value                                            | Comments |

|---------------|--------------------------------------------------|----------|

| Description   | 16 Mbit storage for firmware and power up states | _        |

| Write Cycles  | 75,000 minimum                                   | —        |

#### Power

| Specification | Value             |                      | Comments               |

|---------------|-------------------|----------------------|------------------------|

|               | NI 6535/6536/6537 | NI 6535B/6536B/6537B | Maximum.               |

| +3.3 VDC      | 750 mA            | 1 A                  | Into<br>high-impedance |

| +12 VDC       | 300 mA            | 225 mA               | loads.                 |

| Total power   | 6.1 W             | 6 W                  |                        |

## **Physical Specifications**

| Specification | Value                                                          |                                                                | Comments |

|---------------|----------------------------------------------------------------|----------------------------------------------------------------|----------|

| Dimensions    | PXI Express                                                    | PCI Express                                                    | _        |

|               | 21.4 cm × 2.0 cm × 13.1 cm<br>(8.42 in. × 0.79 in. × 5.14 in.) | 18.1 cm × 2.2 cm × 12.6 cm<br>(7.13 in. × 0.85 in. × 4.93 in.) |          |

| Weight        | 144.58 g (5.1 oz)                                              | 107.7 g (3.8 oz)                                               | —        |

#### Software

| Specification           | Value                                                                                                                                                                                                                                                                   | Comments                                                                                              |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Driver<br>software      | NI 6535: NI-DAQmx driver software version 8.8 or later<br>NI 6536/6537: NI-DAQmx driver software version 8.5 or later<br>NI 6535B/6536B/6537B: NI DAQmx driver software version 9.6.1<br>or later                                                                       | —                                                                                                     |

| Application<br>software | <ul> <li>NI-DAQmx provides programming interfaces for the following application development environments (ADEs):</li> <li>National Instruments LabVIEW</li> <li>National Instruments LabWindows<sup>™</sup>/CVI<sup>™</sup></li> <li>Microsoft Visual Studio</li> </ul> | Refer to the<br>NI-DAQ<br>Readme<br>for more<br>information<br>about<br>supported<br>ADE<br>versions. |

| Test Panel              | National Instruments Measurement & Automation Explorer (MAX) provides test panels with basic acquisition and generation functionality for the NI 6535/6536/6537 and NI 6535B/6536B/6537B. MAX is included on the NI-DAQmx instrument driver media.                      | —                                                                                                     |

#### Environment

**Note** The NI 6535/6536/6537 and NI 6535B/6536B/6537B are intended for indoor use only.

| Specification                     | Value                                                                                                                             | Comments    |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------|

| Operating<br>temperature          | PCI Express: 0 °C to +45 °C<br>PXI Express: 0 °C to +55 °C                                                                        | _           |

| Storage<br>temperature            | -20 °C to +70 °C                                                                                                                  | —           |

| Operating<br>relative<br>humidity | 10% to 90% relative humidity, noncondensing<br>(Meets IEC 60068-2-56.)                                                            | _           |

| Storage<br>relative<br>humidity   | 5% to 95% relative humidity, noncondensing (Meets IEC 60068-2-56.)                                                                | _           |

| Operating shock                   | 30 g, half-sine, 11 ms pulse<br>(Meets IEC 60068-2-27. Test profile developed in accordance<br>with MIL PRF-28800F.)              |             |

| Storage shock                     | 50 g, half-sine, 11 ms pulse<br>(Meets IEC 60068-2-27. Test profile developed in accordance<br>with MIL PRF-28800F.)              | PXI Express |

| Operating vibration               | 5 Hz to 500 Hz, 0.31 g <sub>rms</sub><br>(Meets IEC 60068-2-64.)                                                                  | only        |

| Storage vibration                 | 5 Hz to 500 Hz, 2.46 g <sub>rms</sub><br>(Meets IEC 60068-2-64. Test profile exceeds requirements of<br>MIL PRF-28800F, Class B.) |             |

| Altitude                          | 0 m to 2,000 m above sea level (at 25 °C ambient temperature)                                                                     | _           |

| Pollution<br>Degree               | 2                                                                                                                                 | —           |

# Safety, Electromagnetic Compatibility, and CE Compliance

**Caution** The protection provided by this equipment may be impaired if it is used in a manner not described in this document.

| Specification                                           | Value                                                                                                                                                                                                                                                                                                              | Comments                          |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Safety                                                  | This product is designed to meet the requirements of the following standards of safety for electrical equipment for measurement, control, and laboratory use:                                                                                                                                                      | _                                 |

|                                                         | • IEC 61010-1, EN 61010-1                                                                                                                                                                                                                                                                                          |                                   |

|                                                         | • UL 61010-1, CSA 61010-1                                                                                                                                                                                                                                                                                          |                                   |

| Note: For UL and Certification sect                     | d other safety certifications, refer to the product label or the <i>Online I</i> ion.                                                                                                                                                                                                                              | Product                           |

| Electromagnetic<br>Compatibility                        | This product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:                                                                                                                                                                          | With use of<br>SHC68-C68-D2<br>or |

|                                                         | • EN 61326 (IEC 61326): Class A emissions; Basic immunity                                                                                                                                                                                                                                                          | SHC68-C68-D4<br>shielded cable.   |

|                                                         | • EN 55011 (CISPR 11): Group 1, Class A emissions                                                                                                                                                                                                                                                                  | shielded cable.                   |

|                                                         | AS/NZS CISPR 11: Group 1, Class A emissions                                                                                                                                                                                                                                                                        |                                   |

|                                                         | FCC 47 CFR Part 15B: Class A emissions                                                                                                                                                                                                                                                                             |                                   |

|                                                         | ICES-001: Class A emissions                                                                                                                                                                                                                                                                                        |                                   |

| <b>Note</b> : For the stat<br><i>Certification</i> sect | ndards applied to access the EMC of this product, refer to the Online ion.                                                                                                                                                                                                                                         | e Product                         |

| <b>Note</b> : For EMC of must be installed.             | compliance, device <i>must</i> be operated with shielded cabling. In additi                                                                                                                                                                                                                                        | on, filler panels                 |

| CE Compliance                                           | This product meets the essential requirements of applicable<br>European Directives as follows:                                                                                                                                                                                                                     | —                                 |

| CE                                                      | • 2006/95/EC; Low-Voltage Directive (safety)                                                                                                                                                                                                                                                                       |                                   |

|                                                         | <ul> <li>2004/108/EC; Electromagnetic Compatibility Directive<br/>(EMC)</li> </ul>                                                                                                                                                                                                                                 |                                   |

| Online Product<br>Certification                         | Refer to the product Declaration of Conformity (DoC) for<br>additional regulatory compliance information. To obtain product<br>certifications and the DoC for this product, visit ni.com/<br>certification, search by model number or product line, and<br>click the appropriate link in the Certification column. | _                                 |

| • • •                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ronmental<br>agement NI is committed to designing and manufacturing products in an<br>environmentally responsible manner. NI recognizes that<br>eliminating certain hazardous substances from our products is<br>beneficial to the environment and to NI customers.                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| For additional environmental information, refer to the <i>Minimize</i><br><i>Our Environmental Impact</i> web page at ni.com/<br>environment. This page contains the environmental<br>regulations and directives with which NI complies, as well as<br>other environmental information not included in this document. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>EU Customers</b> : At the end of the product life cycle, all products<br>WEEE recycling center. For more information about WEEE recyc<br>National Instruments WEEE initiatives and compliance with WEE<br>2002/96/EC on Waste Electrical and Electronic Equipment, visit n<br>environment/weee.                    | ling centers,<br>EE Directive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FCerco<br>EVN2e                                                                                                                                                                                                                                                                                                       | for additional environmental information, refer to the <i>Minimize</i><br><i>Dur Environmental Impact</i> web page at ni.com/<br>nvironment. This page contains the environmental<br>egulations and directives with which NI complies, as well as<br>ther environmental information not included in this document.<br><b>EU Customers</b> : At the end of the product life cycle, all products<br>VEEE recycling center. For more information about WEEE recyc<br>lational Instruments WEEE initiatives and compliance with WEE<br>002/96/EC on Waste Electrical and Electronic Equipment, visit n |

#### 电子信息产品污染控制管理办法 (中国 RoHS)

**中国客户** National Instruments 符合中国电子信息产品中限制使用某些有害物质指令 (RoHS)。关于 National Instruments 中国 RoHS 合规性信息,请登录 ni.com/ environment/rohs\_china。(For information about China RoHS compliance, go to ni.com/environment/rohs\_china.)

# Worldwide Support and Services

The National Instruments website is your complete resource for technical support. At ni.com/ support you have access to everything from troubleshooting and application development self-help resources to email and phone assistance from NI Application Engineers.

Visit ni.com/services for NI Factory Installation Services, repairs, extended warranty, and other services.

Visit ni.com/register to register your National Instruments product. Product registration facilitates technical support and ensures that you receive important information updates from NI.

A Declaration of Conformity (DoC) is our claim of compliance with the Council of the European Communities using the manufacturer's declaration of conformity. This system affords the user protection for electromagnetic compatibility (EMC) and product safety. You can obtain the DoC for your product by visiting ni.com/certification. If your product supports calibration, you can obtain the calibration certificate for your product at ni.com/calibration.

National Instruments corporate headquarters is located at 11500 North Mopac Expressway, Austin, Texas, 78759-3504. National Instruments also has offices located around the world. For telephone support in the United States, create your service request at ni.com/support or dial 1 866 ASK MYNI (275 6964). For telephone support outside the United States, visit the Worldwide Offices section of ni.com/niglobal to access the branch office websites, which provide up-to-date contact information, support phone numbers, email addresses, and current events.

Refer to the *NI Trademarks and Logo Guidelines* at ni.com/trademarks for more information on National Instruments trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies. For patents covering National Instruments products/technology, refer to the appropriate location: Help-Patents in your software, the patents.txt file on your media, or the National Instruments Patents Notice at ni.com/patents.You can find information about end-user license agreements (EULAs) and third-party legal notices in the readme file for your NI product. Refer to the *Export Compliance Information* at ni.com/legal/export-compliance for the National Instruments global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data.

© 2006–2014 National Instruments. All rights reserved.