#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

## **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

AT-MIO-16E-2

# **DAQ**

# AT-MIO E Series Register-Level Programmer Manual

Multifunction I/O Boards for the PC AT

#### Internet Support

E-mail: support@natinst.com FTP Site: ftp.natinst.com

Web Address: http://www.natinst.com

#### **Bulletin Board Support**

BBS United States: 512 794 5422 BBS United Kingdom: 01635 551422

BBS France: 01 48 65 15 59

#### Fax-on-Demand Support

512 418 1111

#### Telephone Support (USA)

Tel: 512 795 8248 Fax: 512 794 5678

#### **International Offices**

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Brazil 011 288 3336, Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 09 725 725 11, France 01 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Israel 03 6120092, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico 5 520 2635, Netherlands 0348 433466, Norway 32 84 84 00, Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 200 51 51, Taiwan 02 377 1200, United Kingdom 01635 523545

#### **National Instruments Corporate Headquarters**

6504 Bridge Point Parkway Austin, Texas 78730-5039 USA Tel: 512 794 0100

© Copyright 1995, 1998 National Instruments Corporation. All rights reserved.

# **Important Information**

#### Warranty

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### **Trademarks**

$DAQ-PnP^{TM}$ ,  $DAQ-STC^{TM}$ ,  $NI-DAQ^{TM}$ ,  $RTSI^{TM}$ , and  $SCXI^{TM}$  are trademarks of National Instruments Corporation. Product and company names listed are trademarks or trade names of their respective companies.

#### WARNING REGARDING MEDICAL AND CLINICAL USE OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

# **Contents**

| About This Manual               |                    |     |

|---------------------------------|--------------------|-----|

| Organization of This Manual     |                    | ix  |

|                                 | al                 |     |

| Related Documentation           |                    | xi  |

| Customer Communication          |                    | xi  |

| Chapter 1                       |                    |     |

| General Description             |                    |     |

| General Characteristics         |                    | 1-1 |

| Chapter 2                       |                    |     |

| Theory of Operation             |                    |     |

| Functional Overview             |                    | 2-1 |

| ISA Bus Interface Circuitry     |                    | 2-6 |

| Analog Input and Timing Circuit | try                | 2-8 |

| Analog Input Circuitry          |                    | 2-8 |

| Data Acquisition Timin          | g Circuitry        | 2-1 |

| Single-Read T                   | iming              | 2-1 |

|                                 | on Sequence Timing |     |

|                                 | er Acquisition     |     |

|                                 |                    |     |

|                                 | ıitry              |     |

| Analog Output Circuitry         | y                  | 2-2 |

|                                 | Circuitry          |     |

|                                 | output             |     |

|                                 | neration           |     |

|                                 |                    |     |

| <u> </u>                        |                    |     |

| RTSI Bus Interface Circuitry    |                    | 2-2 |

| Chapter 3                       |                    |     |

| Register Map and Descriptior    | IS                 |     |

| Register Map                    |                    | 3-1 |

| Register Sizes                  |                    | 3-4 |

| Register Descriptions           |                    | 3-4 |

| Misc Register Group             |                    | 3-4 |

| Serial Comma                    | nd Register        | 3-5 |

| Misc Command Register               | 3-6  |

|-------------------------------------|------|

| Status Register                     |      |

| Analog Input Register Group         |      |

| ADC FIFO Data Register              |      |

| Configuration Memory Low Register   |      |

| Configuration Memory High Register  |      |

| Analog Output Register Group        |      |

| AO Configuration Register           | 3-16 |

| DAC FIFO Data Register              |      |

| DAC0 Direct Data Register           |      |

| DAC1 Direct Data Register           |      |

| DMA Control Register Group          | 3-21 |

| Strobes Register                    | 3-21 |

| Channel A Mode Register             | 3-22 |

| Channel B Mode Register             | 3-23 |

| Channel C Mode Register             | 3-24 |

| AI AO Select Register               | 3-25 |

| G0 G1 Select Register               |      |

| DIO Register Group                  |      |

| DAQ-STC Register Group              | 3-27 |

| FIFO Strobe Register Group          | 3-27 |

| Configuration Memory Clear Register | 3-27 |

| ADC FIFO Clear Register             | 3-27 |

| DAC FIFO Clear Register             | 3-27 |

| Ohantay 4                           |      |

| Chapter 4                           |      |

| Programming                         |      |

| Plug and Play Initialization        | 4-2  |

| Windowing Registers                 |      |

| Programming Examples                | 4-4  |

| Digital I/O                         | 4-5  |

| Example 1                           | 4-5  |

| Example 2                           | 4-6  |

| Analog Input                        | 4-6  |

| Example 1                           | 4-7  |

| Example 2                           | 4-10 |

| Example 3                           | 4-12 |

| Example Program                     | 4-13 |

| Example 4                           | 4-15 |

| Example 5                           | 4-18 |

| Example 6                           | 4-20 |

| Example 7                           | 4-22 |

|                                              | Exam                  | ple 8                                          | 4-24 |

|----------------------------------------------|-----------------------|------------------------------------------------|------|

|                                              | Exam                  | iple 9                                         | 4-26 |

| Analog                                       | g Output              | t                                              | 4-29 |

|                                              | Exam                  | ple 1                                          | 4-30 |

|                                              | Exam                  | ple 2                                          | 4-31 |

|                                              | Exam                  | pple 3                                         | 4-36 |

|                                              | Exam                  | ple 4                                          | 4-38 |

|                                              | Exam                  |                                                |      |

|                                              | Example 9             |                                                |      |

| Genera                                       |                       |                                                |      |

|                                              |                       |                                                |      |

|                                              |                       |                                                |      |

|                                              |                       |                                                |      |

|                                              |                       |                                                |      |

|                                              |                       |                                                |      |

|                                              |                       |                                                |      |

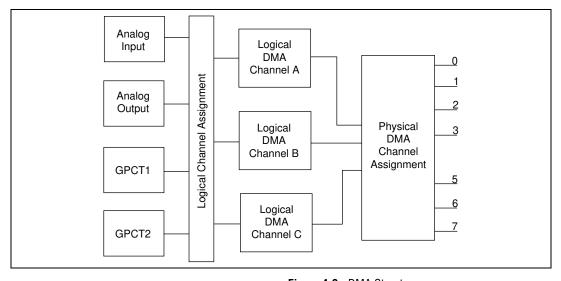

| DMA                                          |                       |                                                |      |

|                                              | Single                | e Channel Versus Dual Channel DMA              | 4-54 |

| Calibration<br>Appendix A<br>OKI MSM82       | EEPR<br>Calib<br>NI-D | ration DACsAQ Calibration Function             | 5-8  |

| Appendix B<br>Customer (                     |                       | unication                                      |      |

| Glossary                                     |                       |                                                |      |

| ndex                                         |                       |                                                |      |

| <b>Figures</b><br>Figure<br>Figure<br>Figure | 2-2.                  | AT-MIO-16E-10 and AT-MIO-16DE-10 Block Diagram | 2-2  |

|                                              |                       |                                                |      |

|       | Figure 2-4.  | AT-AI-16XE-10 Block Diagram                                   | 2-4  |

|-------|--------------|---------------------------------------------------------------|------|

|       | Figure 2-5.  | AT-MIO-16XE-50 Block Diagram                                  | 2-5  |

|       | Figure 2-6.  | ISA Bus Interface Circuitry Block Diagram                     |      |

|       | Figure 2-7.  | Analog Input and Data Acquisition Circuitry Block Diagram     | 2-8  |

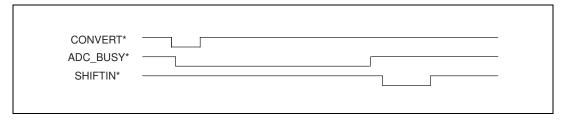

|       | Figure 2-8.  | ADC Timing                                                    |      |

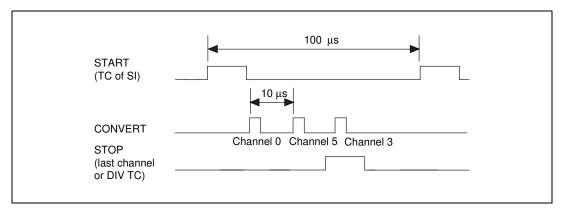

|       | Figure 2-9.  | Timing of Scan in Example 1                                   | 2-13 |

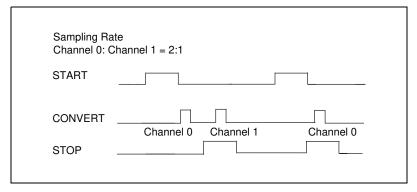

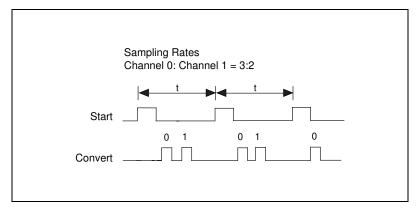

|       | Figure 2-10. | Multirate Scanning of Two Channels                            | 2-14 |

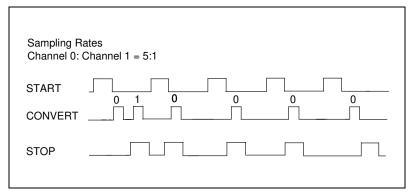

|       | Figure 2-11. | Multirate Scanning of Two Channels with 1:x Sampling Rate     | 2-15 |

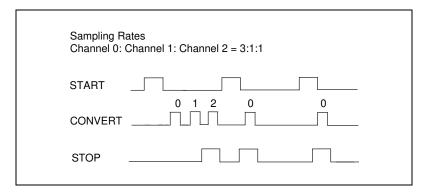

|       | Figure 2-12. | Multirate Scanning of Two Channels with 3:1:1 Sampling Rate   | 2-15 |

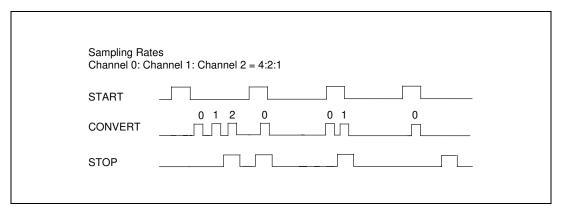

|       | Figure 2-13. | Multirate Scanning of Three Channels with 4:2:1 Sampling Rate | 2-15 |

|       | Figure 2-14. | Multirate Scanning without Ghost                              | 2-16 |

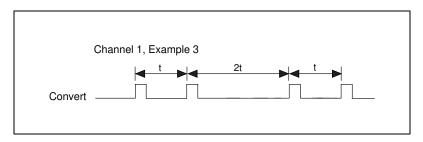

|       | Figure 2-15. | Occurrences of Conversion on Channel 1 in Example 3           | 2-16 |

|       | Figure 2-16. | Successive Scans Using Ghost                                  | 2-17 |

|       | Figure 2-17. | Analog Output Circuitry Block Diagram                         |      |

|       | Figure 2-18. | DAQ-STC Counter Diagram                                       | 2-24 |

|       | Figure 2-19. | RTSI Bus Interface Circuitry Block Diagram                    | 2-25 |

|       | Figure 4-1.  | Analog Trigger Structure                                      | 4-50 |

|       | Figure 4-2.  | DMA Structure                                                 | 4-53 |

|       | Figure 5-1.  | EEPROM Read Timing                                            | 5-2  |

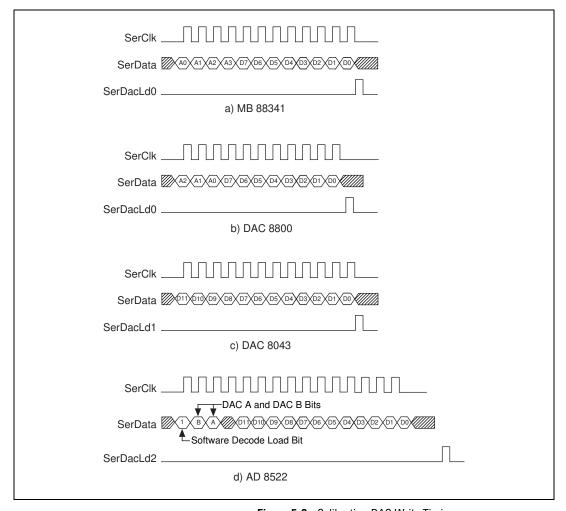

|       | Figure 5-2.  | Calibration DAC Write Timing                                  | 5-9  |

| Table | :S           |                                                               |      |

|       | Table 1-1.   | Features of the AT E Series Boards                            | 1-2  |

|       | Table 2-1.   | Analog Input Configuration Memory                             | 2-17 |

|       | Table 3-1.   | AT E Series Register Map                                      | 3-2  |

|       | Table 3-2.   | AT E Series Windowed Register Map                             | 3-3  |

|       | Table 3-3.   | PGIA Gain Selection                                           | 3-11 |

|       | Table 3-4.   | Calibration Channel Assignments                               | 3-13 |

|       | Table 3-5.   | Differential Channel Assignments                              | 3-14 |

|       | Table 3-6.   | Nonreferenced Single-Ended Channel Assignments                | 3-14 |

|       | Table 3-7.   | Referenced Single-Ended Channel Assignments                   | 3-15 |

|       | Table 3-8.   | Channel Assignments                                           | 3-16 |

|       | Table 5-1.   | AT-MIO-16E-1, AT-MIO-16E-2, AT-MIO-64E-3 EEPROM Map           | 5-2  |

|       | Table 5-2.   | AT-MIO-16E-10 and AT-MIO-16DE-10 EEPROM Map                   |      |

|       | Table 5-3.   | AT-MIO-16XE-50 EEPROM Map                                     | 5-5  |

|       | Table 5-4.   | AT-MIO-16XE-10 and AT-AI-16XE-10 EEPROM Map                   | 5-7  |

# About This Manual

This manual describes the registers and register map of the AT E Series boards and contains information concerning their register-level programming.

The DAQ-STC, a National Instruments system timing controller ASIC, is the timing engine that drives the AT E Series boards. Consequently, the timing and programming sections in this manual repeat certain information from, or draw your attention to, sections in the *DAQ-STC Technical Reference Manual*. You must use your register-level programmer manual along with the *DAQ-STC Technical Reference Manual* for a complete understanding of AT E Series board programming.

Unless otherwise noted, text applies to all boards in the AT E Series. The AT E Series boards are:

- AT-MIO-16E-1

- AT-MIO-16E-2

- AT-MIO-64E-3

- AT-MIO-16E-10

- AT-MIO-16DE-10

- AT-MIO-16XE-10

- AT-AI-16XE-10

- AT-MIO-16XE-50

The AT E Series boards are high-performance multifunction analog, digital, and timing I/O boards for the IBM PC AT series computers. Supported functions include analog input, analog output, digital I/O, and timing I/O.

# **Organization of This Manual**

The AT-MIO E Series Register-Level Programmer Manual is organized as follows:

- Chapter 1, General Description, describes the general characteristics of the AT E Series boards.

- Chapter 2, *Theory of Operation*, contains a functional overview of the AT E Series board and explains the operation of each functional unit making up the AT E Series boards.

- Chapter 3, Register Map and Descriptions, describes in detail the address and function of each of the AT E Series control and status registers.

- Chapter 4, *Programming*, contains programming instructions for operating the circuitry on the AT E Series board.

- Chapter 5, *Calibration*, explains how to calibrate the analog input and output sections of the AT E Series boards by reading calibration constants from the EEPROM and writing them to the calibration DACs.

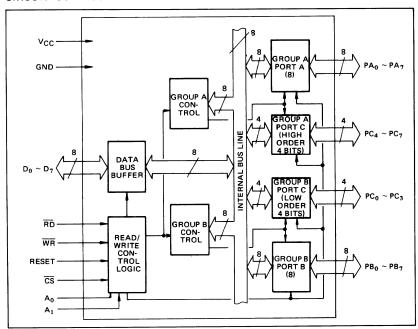

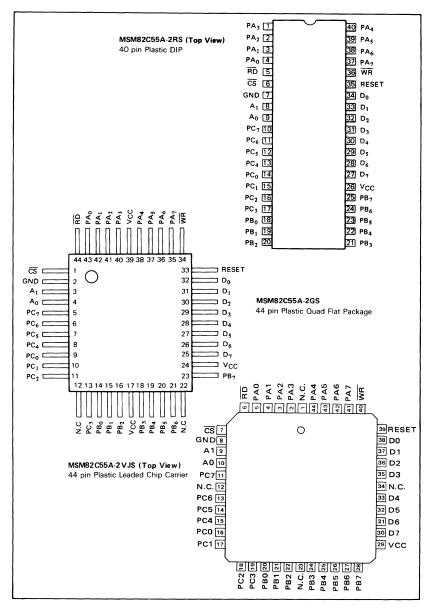

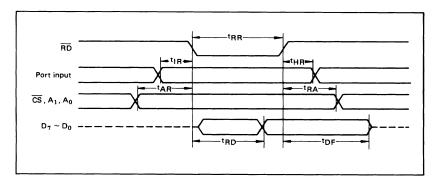

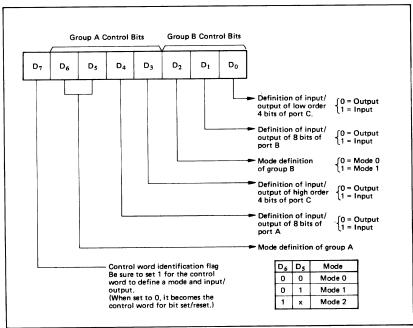

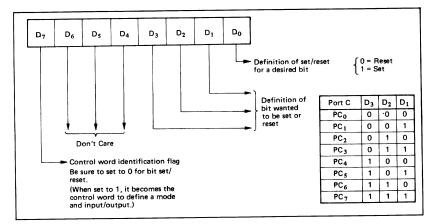

- Appendix A, OKI MSM82C55A Data Sheet, contains a manufacturer data sheet for the MSM82C55A CMOS programmable peripheral interface (OKI Semiconductor).

- Appendix B, Customer Communication, contains forms for you to complete to help you communicate with National Instruments about our products.

- The Glossary contains an alphabetical list and description of terms used in this manual, including acronyms, abbreviations, metric prefixes, mnemonics, and symbols.

- The *Index* alphabetically lists topics covered in this manual, including the page where you can find the topic.

## **Conventions Used in This Manual**

The following conventions are used in this manual:

Angle brackets containing numbers separated by an ellipsis represent a range of values associated with a bit, port, or signal name (for example, ACH<0..7> stands for ACH0 through ACH7).

This icon to the left of bold italicized text denotes a note, which alerts you to important information.

Bold italic text denotes a note, caution, or warning.

Italic text denotes variables, emphasis, a cross reference, or an introduction to a key concept. This font also denotes text from which you supply the appropriate word or value, as in NI-DAQ 6.x.

italic

<>

bold italic

monospace

Text in this font denotes text or characters that you should literally enter from the keyboard, sections of code, programming examples, and syntax examples. This font is also used for the proper names of disk drives, paths, directories, programs, subprograms, subroutines, device names, functions, operations, variables, filenames and extensions, and for statements and comments taken from programs.

PC

PC refers to the IBM PC AT and compatible computers.

## **Related Documentation**

You may find the following National Instruments documents helpful for programming interrupts and DMA:

- Programming Interrupts for Data Acquisition on 80x86-Based Computers, Application Note 010

- Programming DMA on PC/XT/AT Computers, Application Note 029

The following National Instruments manuals contain general information and operating instructions for the AT E Series boards:

- AT E Series User Manual

- DAQ-STC Technical Reference Manual

## **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix B, *Customer Communication*, at the end of this manual.

# **General Description**

This chapter describes the general characteristics of the AT E Series boards.

## **General Characteristics**

The AT E Series boards are completely Plug and Play-compatible multifunction analog, digital, and timing I/O boards for the PC AT and compatible computers. This family of boards features 12-bit and 16-bit ADCs with 16 and 64 analog inputs, 12-bit and 16-bit DACs with voltage outputs, eight and 32 lines of TTL-compatible digital I/O, and two 24-bit counter/timers for timing I/O. Because the AT E Series boards have no DIP switches, jumpers, or potentiometers, they are easily configured and calibrated using software.

The AT E Series boards are the first completely switchless and jumperless DAQ boards. This feature is made possible by the National Instruments DAQ-PnP bus interface chip to connect the board to the AT I/O bus. The DAQ-PnP implements the Plug and Play ISA Specification so that the DMA, interrupts, and base I/O addresses are all software configurable. This allows you to easily change the AT E Series board configuration without having to remove the board from your computer.

The AT E Series boards use the National Instruments DAQ-STC system timing controller for time-related functions. The DAQ-STC consists of three timing groups that control analog input, analog output, and general-purpose counter/timer functions. These groups include a total of seven 24-bit and three 16-bit counters and a maximum timing resolution of 50 ns.

A common problem with DAQ boards is that you cannot easily synchronize several measurement functions to a common trigger or timing event. The AT E Series boards have the Real-Time System Integration (RTSI) bus to solve this problem. The RTSI bus consists of our RTSI bus interface and a ribbon cable to route timing and trigger signals between several functions on up to five DAQ boards in your PC.

The AT E Series boards can interface to an SCXI system so that you can acquire over 3,000 analog signals from thermocouples, RTDs, strain gauges, voltage sources, and current sources. You can also acquire or generate digital signals for communication and control. SCXI is the instrumentation front end for plug-in DAQ boards.

Refer to Table 1-1 for a listing of the various boards in the AT E Series and their distinguishing features.

**Table 1-1.** Features of the AT E Series Boards

| Board          | Features                                                                                                                                            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| AT-MIO-16E-1   | 16 single-ended or eight differential 12-bit analog inputs, 1,250 kS/s, two 12-bit analog outputs, eight digital I/O, analog and digital triggering |

| AT-MIO-16E-2   | 16 single-ended or eight differential 12-bit analog inputs, 500 kS/s, two 12-bit analog outputs, eight digital I/O, analog and digital triggering   |

| AT-MIO-64E-3   | 64 single-ended or 32 differential 12-bit analog inputs, 500 kS/s, two 12-bit analog outputs, eight digital I/O, analog and digital triggering      |

| AT-MIO-16E-10  | 16 single-ended or eight differential 12-bit analog inputs, 100 kS/s, two 12-bit analog outputs, eight digital I/O, digital triggering              |

| AT-MIO-16DE-10 | 16 single-ended or eight differential 12-bit analog inputs, 100 kS/s, two 12-bit analog outputs, 32 digital I/O, digital triggering                 |

| AT-MIO-16XE-10 | 16 single-ended or eight differential 16-bit analog inputs, 100 kS/s, two 16-bit analog outputs, eight digital I/O, analog and digitial triggering  |

| AT-MIO-16XE-50 | 16 single-ended or eight differential 16-bit analog inputs, 20 kS/s, two 12-bit analog outputs, eight digital I/O, digital triggering               |

| AT-AI-16XE-10  | 16 single-ended or eight differential 16-bit analog inputs, 100 kS/s, eight digital I/O, analog and digital triggering                              |

Your AT E Series board is completely software configurable. Refer to your AT E Series User Manual if you have not already installed and configured your board.

# **Theory of Operation**

This chapter contains a functional overview of the AT E Series boards and explains the operation of each functional unit making up the AT E Series boards.

## **Functional Overview**

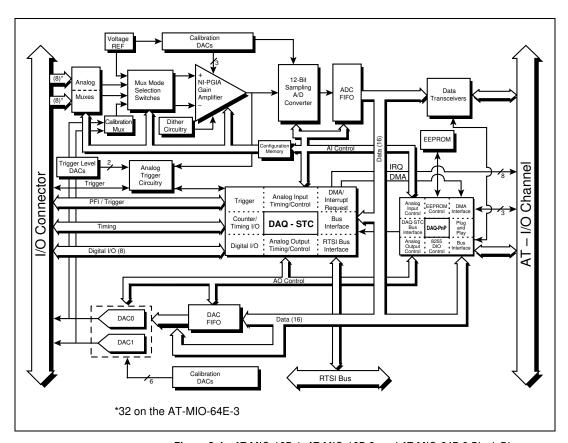

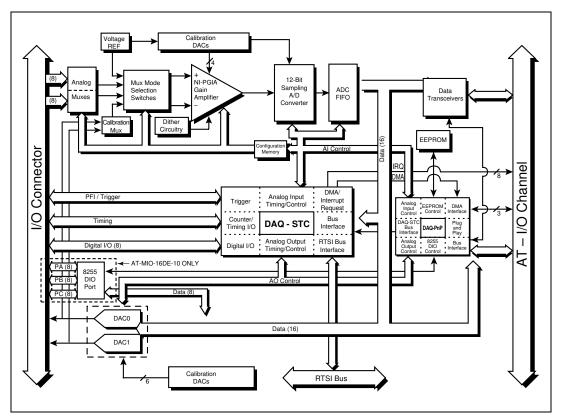

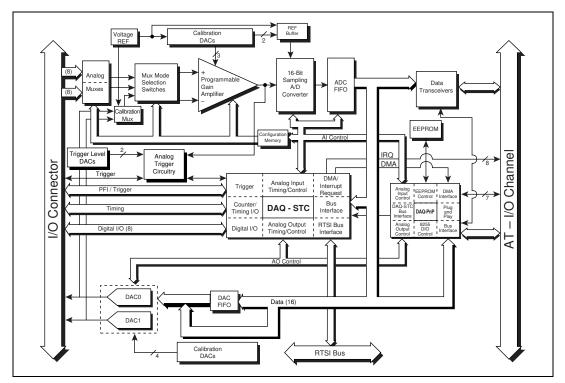

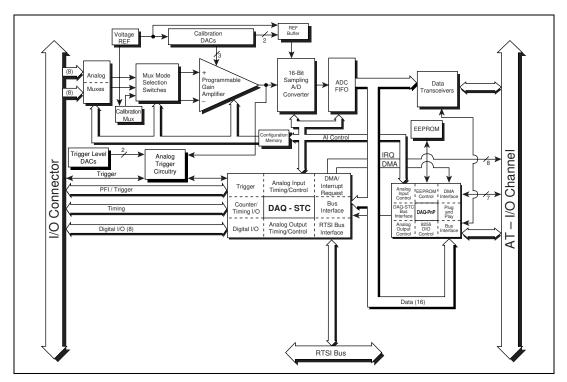

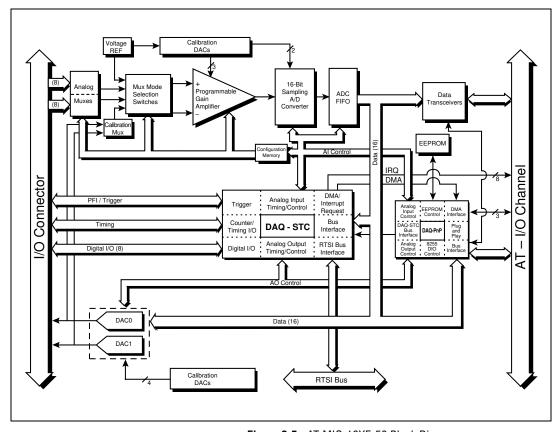

The block diagram in Figures 2-1 through 2-5 give a functional overview of each AT E Series board.

Figure 2-1. AT-MIO-16E-1, AT-MIO-16E-2, and AT-MIO-64E-3 Block Diagram

Figure 2-2. AT-MIO-16E-10 and AT-MIO-16DE-10 Block Diagram

Figure 2-3. AT-MIO-16XE-10 Block Diagram

Figure 2-4. AT-AI-16XE-10 Block Diagram

Figure 2-5. AT-MIO-16XE-50 Block Diagram

The following major components make up the AT E Series boards:

- ISA bus interface circuitry with Plug and Play capability (DAQ-PnP)

- Analog input circuitry

- Analog trigger circuitry

- Analog output circuitry

- Digital I/O circuitry

- Timing I/O circuitry (DAQ-STC)

- RTSI bus interface circuitry

The internal data and control buses interconnect the components. Notice that the DAQ-STC is the timing engine that provides precise timing signals for the analog input and output operations. The timing I/O circuitry information in this manual is skeletal in nature and is sufficient in most

cases. For register-level programming information, refer to the *DAQ-STC Technical Reference Manual*.

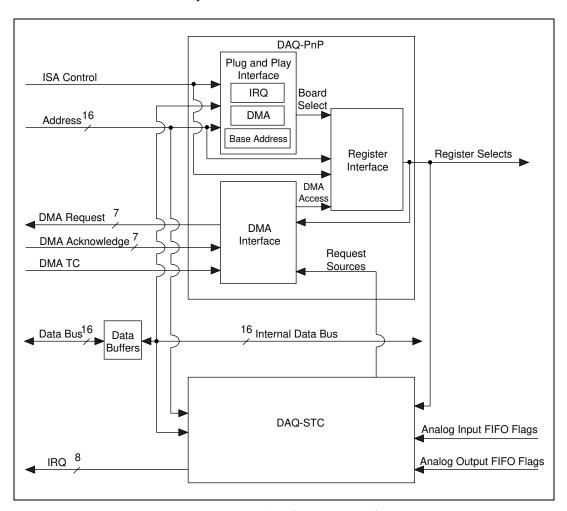

# **ISA Bus Interface Circuitry**

The AT E Series boards are all full-size, 16-bit ISA I/O interface cards. The ISA bus features a 16-bit address bus, a 16-bit data bus, a DMA arbitration bus, interrupt lines, and several control and support signals. Figure 2-6 shows the functional blocks making up the AT E Series ISA bus interface circuitry.

Figure 2-6. ISA Bus Interface Circuitry Block Diagram

The DAQ-PnP provides the main interface to the ISA bus, including support for the Plug and Play ISA Specification. Plug and Play provides a mechanism for assigning bus resources to the card using software only. This eliminates the need for setting jumpers or DIP switches on the board to select the base I/O address, interrupt lines, and DMA channels. In a Plug and Play aware system, the Plug and Play circuitry in the DAQ-PnP can request a base I/O address, up to three DMA channels, and up to two interrupt lines from the configuration manager. In other systems, application software can simply assign particular resources to the card.

The DAQ-PnP stores the resource assignments in the Plug and Play configuration registers. It also performs the base I/O address decoding after the board is activated through software. The DAQ-PnP performs full 16-bit address decoding, where address lines SA<15..5> are used for the comparison. This decoding allows the board to be located on any 32-byte boundary within the 16-bit address space. The remaining address lines SA<4..0> are used to select the onboard registers.

The register interface block within the DAQ-PnP is used to select the target register of a particular read or write cycle. These accesses are controlled by the base address decoding, SA<4..0> and the ISA control lines when the CPU is trying to access the board. In the case of DMA transfers, the access is controlled by the DMA block within the DAQ-PnP and the ISA control lines. The register interface block provides all access to the registers in the DAQ-PnP, DAQ-STC, and other onboard resources such as the FIFOs.

The DMA interface block within the DAQ-PnP provides for high-speed data transfer between the board and the system memory. Up to three DMA channels can be used simultaneously for data transfers with analog input, analog output, and the general-purpose counters. The DMA circuitry can only perform 16-bit transfers—DMA channels 5, 6, and 7 are available in ISA computers, whereas channels 0, 1, 2, 3, 5, 6, and 7 are available in EISA computers. The DMA transfers are initiated by the DAQ-STC, which indicates to the DAQ-PnP when the data transfers should occur. The DAQ-PnP then asserts the appropriate DMA request line and performs the transfer when the DMA acknowledge occurs.

The DAQ-STC can generate interrupts from over 20 sources and can route these interrupts to one or two of eight interrupt lines on the ISA bus interface. The use of two interrupt lines can improve performance in some environments but is usually more difficult to program. The AT E Series boards connect the eight DAQ-STC interrupt lines (0..7) to the IRQ3, 4, 5, 7, 10, 11, 12, and 15 lines, respectively.

The data buffers are used to control the direction of the data transfers on the bi-directional data lines based on whether the transfer is a read or write operation. The enabling and direction of the buffers is controlled by the DAQ-PnP.

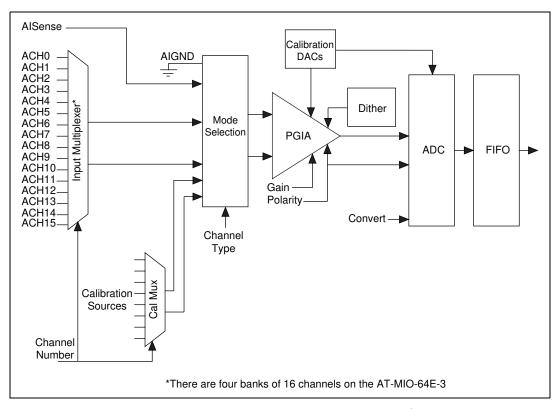

# **Analog Input and Timing Circuitry**

The AT E Series boards have 16 to 64 analog input channels and a timing core within the DAQ-STC that is dedicated to analog input operation. Figure 2-7 shows a general block diagram for the analog input circuitry.

Figure 2-7. Analog Input and Data Acquisition Circuitry Block Diagram

## **Analog Input Circuitry**

The general model for analog input on the AT E Series boards includes input multiplexer, multiplexer mode selection switches, a software-programmable gain instrumentation amplifier, calibration

hardware, a sampling ADC, a 16-bit wide data FIFO, and a configuration memory.

The configuration memory defines the parameters to use for each conversion. Each entry in the configuration memory includes channel type, channel number, bank, gain, polarity, dither, general trigger, and last channel. The configuration memory is a 512-entry deep FIFO that is initialized prior to the start of the acquisition sequence. It can be incremented after every conversion, allowing the analog input configuration to vary on a per conversion basis. Once the FIFO is empty, the DAQ-STC asserts the FIFO retransmit signal, which restores the FIFO data to its original state.

The channel type field indicates the resource type to be used during the conversion and controls the multiplexer mode selection switches. These resources include calibration channels, analog input channels in differential, referenced single-ended, or nonreferenced single-ended mode, or a ghost channel. The ghost type indicates that a conversion should occur but that the data should not be stored in the data FIFO. This type is useful for multirate scanning, which is described later in this chapter.

The channel number indicates which channel of the specified type will be used during the conversion, while the bank field indicates which bank of 16 channels is active. This bank field is used on boards that have more than 16 channels. These bits control the input multiplexers.

The programmable gain instrumentation amplifier (PGIA) serves two purposes on the AT E Series boards. The PGIA applies gain to the input signal, amplifying an analog input signal before sampling and conversion to increase measurement resolution and accuracy. This gain is determined by the gain field in the configuration memory. It also provides polarity selection for the input signal, which is also controlled by the configuration memory. In unipolar mode, the input range includes only positive voltages. In bipolar mode, the input signal may also be a negative voltage. The PGIA provides gains of 0.5, 1, 2, 5, 10, 20, 50, and 100, except on the AT-MIO-16XE-50, AT-MIO-16XE-10, and AT-AI-16XE-10. On the AT-MIO-16XE-50 and AT-AI-16XE-10, the PGIA supports gains of 1, 2, 10, 20, 50, and 100.

The dither circuitry adds approximately 0.5 LSB rms of white Gaussian noise to the signal to be converted by the ADC. This addition is useful for applications, such as calibration, involving averaging to increase the resolution of the board to more than the resolution of the ADC. In such applications, which are often lower frequency in nature, adding the dither

decreases noise modulation and improves differential linearity. Dither should be disabled for high-speed applications not involving averaging because it would only add noise. When taking DC measurements, such as when calibrating the board, you should enable dither and average about 1,000 points to take a single reading. This process removes the effects of quantization, reduces measurement noise, and improves resolution. Notice that dither cannot be disabled on the AT-MIO-16XE-50, AT-MIO-16XE-10, and AT-AI-16XE-10.

The last channel bit is used to indicate that this is the last conversion in a scan. The DAQ-STC will end the scan on the conversion with this bit set.

The AT E Series boards use sampling, successive approximation ADCs with 12 or 16 bits of resolution with maximum conversion rates between 50  $\mu$ s and 800 ns. The converter can resolve its input range into 4,096 different steps for the 12-bit ADC and 65,536 for the 16-bit ADC. The input range of the 12-bit boards is  $\pm 5$  V in bipolar mode and 0 to  $\pm 10$  V in unipolar mode. These modes correspond to ranges of  $\pm 200$ ,047 in unipolar mode and 0 to 4,095 in bipolar mode. The input range of the 16-bit boards is  $\pm 10$  V in bipolar mode and 0 to  $\pm 10$  V in unipolar mode. These modes correspond to ranges of  $\pm 320$ ,768 to 32,767 in bipolar mode and 0 to 65,535 in unipolar mode.

The AT E Series boards include a 16-bit wide FIFO to buffer the analog input data. This buffering will increase the maximum rate that the analog input can sustain during continuous acquisition. The FIFO is 8 kwords deep on the AT-MIO-16E-1, 2 kwords deep on the AT-MIO-16E-2 and AT-MIO-64E-3, and 512 words deep on the others. The DAQ-STC shifts the data into the FIFO from the ADC when the conversion is complete. This buffering allows the ADC to begin a new conversion even though the data has not yet been read from the board. This buffering also provides more time for the software or DMA to respond and read the analog input data from the board. If the FIFO is full and another conversion completes, an error condition called *FIFO overflow* occurs and the data from that conversion is lost. The FIFO not empty, half-full, and full flags are available to generate interrupts or DMA requests for the data transfer.

Measurement reliability is assured through the onboard calibration circuitry of the board. This circuitry uses an internal, stable 5 V reference that is measured at the factory against a higher accuracy reference; its value is then stored in the EEPROM. With this stored reference value, the board can be recalibrated at any time under any number of different environmental conditions in order to remove errors caused by time and temperature drift. The EEPROM stores calibration constants that can be

read and then written to calibration DACs that adjust input offset, output offset, and gain errors associated with the analog input section. When the board leaves the factory, the upper one-fourth of the EEPROM is protected and cannot be overwritten. The lower three-fourths is unprotected and the top fourth of that can be used to store alternate calibration constants for the different conditions under which you use the board. The entire lower half of the EEPROM is used for storing Plug and Play information and should never be written to.

## **Data Acquisition Timing Circuitry**

This section describes the different methods of acquiring A/D data from a single channel or multiple channels.

From this section through the end of this manual, you are assumed to have a working knowledge of the DAQ-STC features. These features are explained in the *DAQ-STC Technical Reference Manual*. If you have not read the functional description of each DAQ-STC module, you must do so before completing this register-level programmer manual.

## **Single-Read Timing**

To acquire data from the ADC, initiate a single conversion and read the resulting value from the ADC FIFO buffer after the conversion is complete. You can generate a single conversion in three different ways—apply an active low pulse to the CONVERT\* pin of the I/O connector, generate a falling edge on the sample-interval counter of the DAQ-STC, or strobe the appropriate bit in a register in the AT E Series register set. Any one of these operations will generate the timing shown in Figure 2-8.

Figure 2-8. ADC Timing

When SHIFTIN\* shifts the ADC value into the ADC FIFO buffer, the AI\_FIFO\_Empty\_St bit in the status register is cleared, which indicates that valid data is available to be read. Single conversion timing of this type is appropriate for reading channel data on an *ad hoc* basis. However, if you need a sequence of conversions, the time interval between successive

conversions is not constant because it relies on the software to generate the conversions. For finely timed conversions that require triggering and gating, you must program the boards to automatically generate timed signals that initiate and gate conversions. This is known as a data acquisition sequence.

### **Data Acquisition Sequence Timing**

The following counters are used for a data acquisition sequence:

Scan interval (SI) 24 bits

Sample interval (SI2) 16 bits

Divide by (DIV) 16 bits

Scan counter (SC) 24 bits

This section presents a concise summary of only the most important features of your board. For a complete description of all the analog input modes and features of the AT E Series, refer to the *DAQ-STC Technical Reference Manual*.

The most basic timing signal in the analog input model is the CONVERT\* signal. A group of precisely timed CONVERT\* pulses is a SCAN. The sequence of channels selected in each conversion in a SCAN is programmed in the configuration memory prior to starting the operation. The SI2 counter is a 16-bit counter in the DAQ-STC. This counter determines the interval between CONVERT\* pulses. It can be programmed for a maximum interval of 3.3 ms and a minimum interval of 50 ns. If alternate slow timebases are used, the maximum interval is 0.65 s. Each time the counter reaches terminal count (TC), a CONVERT\* pulse is generated. Alternatively, CONVERT\* pulses could be given externally.

A SCAN sequence is started by the START pulse, which is generated by the terminal count of the SI counter. This counter is a 24-bit counter that determines the time between the start of each SCAN. The minimum duration is 50 ns and the maximum duration is 0.8 s when the internal 20 MHz timebase is used. If the internal 100 kHz timebase is used, the maximum is 167 s. The START pulse triggers the SI2 counter to generate CONVERT\* pulses. With each conversion, the configuration memory advances by one and selects the next set of analog input conditions—channel number, gain, polarity, etc. A STOP pulse ends the SCAN sequence. This STOP could be generated in two ways—either by using the LASTCHANNEL bit in the configuration memory or by programming the 16-bit DIV counter to count the number of conversions per SCAN and using the terminal count of the DIV counter as a STOP pulse.

The SC is a 24-bit counter that counts the number of scans. The data acquisition sequence can be programmed to stop when the terminal count of this counter is reached. Notice that the START and STOP signals could also be supplied externally.

Example 1: To acquire 50 scans, with each scan consisting of one sample on channel 0 at gain 50, one sample on channel 5 at gain 2, and one sample on channel 3 at gain 10, with a SCAN interval of 100  $\mu$ s and a sample interval of 10  $\mu$ s, program your configuration memory as follows:

- 1. channel 0, gain 50

- 2. channel 5, gain 2

- 3. channel 3, gain 10, last channel

You should program SI2 for  $10 \,\mu s$ , SI for  $100 \,\mu s$ , and SC for  $50 \,(50 \,scans)$ . Figure 2-9 shows the timing for each scan in Example 1.

Figure 2-9. Timing of Scan in Example 1

The START pulse starts each scan. The first CONVERT pulse samples channel 0, the second CONVERT pulse samples channel 5, and the third CONVERT pulse samples channel 3. The STOP pulse ends the scan.

Example 1 allows you to sample all three channels at a rate of 10 kS/s per channel ( $100 \,\mu\text{s}$  sample interval period). To achieve different rates for different channels, you must do multirate scanning.

#### **Multirate Scanning without Using Ghost**

Example 2: To sample channel 0 at 10 kS/s and channel 1 at 5 kS/s, both at gain 1 with 50 scans, program the configuration memory as follows:

- channel 0, gain 1

- 2. channel 1, gain 1, last channel

- 3. channel 0, gain 1, last channel

Program SI for 100  $\mu$ s, SI2 for 10  $\mu$ s. Figure 2-10 shows the timing sequence for two scans.

Figure 2-10. Multirate Scanning of Two Channels

This sequence of two scans is repeated 25 times to complete the acquisition. Notice that channel 0 is sampled once every 100  $\mu$ s. Hence, its sampling rate is 10 kS/s, whereas channel 1 is sampled once every 200  $\mu$ s. Its rate is 5 kS/s. Similarly, you could implement any 1:x ratio of sampling rates.

The effective scan interval of the slower channel will be at  $\frac{1}{x}$  the rate of

the faster channel. This implementation requires x scan sequences in the configuration memory.

Also, you can implement a 1:1:x or 1:x:mx ratio for three channels, where m is a non-negative integer. Figures 2-11, 2-12, and 2-13 show timing sequences for different ratios. In these figures, the numbers above the CONVERT pulses indicate the channels sampled in that conversion.

**Figure 2-11.** Multirate Scanning of Two Channels with 1:*x* Sampling Rate

Figure 2-12. Multirate Scanning of Two Channels with 3:1:1 Sampling Rate

Here, channel 0 is sampled three times, whereas channels 1 and 2 are sampled once every three scans.

Figure 2-13. Multirate Scanning of Three Channels with 4:2:1 Sampling Rate

#### **Multirate Scanning Using Ghost**

If the ghost option in the configuration memory is set, that conversion occurs but the data is not stored in the analog input FIFO. In other words, a conversion is performed and the data is thrown away. By using this option, multirate scanning with ratios such as x:y are possible, within the limits imposed by the size of the configuration memory.

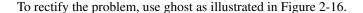

Figure 2-14 and 2-16 illustrate the advantages of using the ghost feature. Figure 2-12 shows example 3 timing, and Figure 2-16 shows the same example using ghost.

Example 3: channel 1: channel 0 = 2:3 (without ghost).

Figure 2-14. Multirate Scanning without Ghost

In example 3, channel 0 is sampled correctly. Although channel 1 is sampled twice, it does not yield a 50% duty cycle. This type of acquisition will result in imprecise rates. Figure 2-15 shows the relative occurrences of convert pulses in Figure 2-14.

Figure 2-15. Occurrences of Conversion on Channel 1 in Example 3.

Figure 2-16. Successive Scans Using Ghost

The shaded conversions are ghost conversions. The short arrows indicate channel 0 samples and the long arrows indicate channel 1 samples that are actually stored in the FIFOs.

Table 2-1 shows what the configuration memory would look like.

| Channel | Ghost | Last Channel |

|---------|-------|--------------|

| 0       | _     | _            |

| 1       | _     | last channel |

| 0       | ghost | _            |

| 1       | ghost | last channel |

| 0       | ghost | _            |

| 1       | _     | last channel |

| 0       | _     | _            |

| 1       | ghost | last channel |

| 0       | ghost | _            |

| 1       | _     | last channel |

| 0       | ghost | _            |

| 1       | ghost | last channel |

**Table 2-1.** Analog Input Configuration Memory

The symbol — indicates that ghost or last channel is absent.

Now both channel 0 and channel 1 are sampled with 50% duty cycle.

## Posttrigger and Pretrigger Acquisition

Whereas a data acquisition operation normally ends when the SC counts down to zero, it can be initiated either through software, by strobing a bit in a control register in the DAQ-STC, or by suitable external triggers.

There are two internal trigger lines—START1 and START2. These appear at the connector on pins called PFI0/Trig1 and PFI1/Trig2, respectively. START1 is used as a trigger line in the posttrigger mode. Since the START1 pulse can be generated through software by strobing a bit, all of the examples discussed so far can be generally categorized as posttrigger acquisition. In the classic posttrigger mode case, the data acquisition circuitry is armed by software but does not start acquiring data until a pulse is given on the START1 line. Then the acquisition starts and ends when the SCAN counter counts down to zero.

In the pretrigger mode, data is acquired before and after the trigger. In this mode, both START1 and START2 lines are used. There are two counts for the SCAN counter—the pretrigger count and the posttrigger count. To begin with, the pretrigger count is loaded into the SC. Acquisition is then started through either software by strobing a bit, or through hardware by externally pulsing the START1 pin of the connector. Acquisition then starts and data is acquired. When the SC counts down to zero, the scans continue and data still gets acquired. During this time, the board waits for a START2 pulse but the SC does not count. Also, the SC gets loaded with the posttrigger count. When a START2 pulse is received, the SC once again starts counting. When it reaches zero, the operation ends. Refer to the *Acquisition Level Timing and Control* section of Chapter 2 in the *DAQ-STC Technical Reference Manual* for timing examples of pretrigger and posttrigger modes.

#### Variations:

- Posttrigger and pretrigger modes can be retriggerable. This means that

after one posttrigger or pretrigger operation is over, the SC gets

reloaded and the board sits waiting for an additional START1. This can

continue indefinitely and can be disabled through software.

- A special mode in the DAQ-STC allows continuous software-initiated acquisition to continue indefinitely. In this mode, the SC gets reloaded each time it counts down to zero. The acquisition can be stopped by disarming the SC. When the SC counts down to zero, acquisition stops.

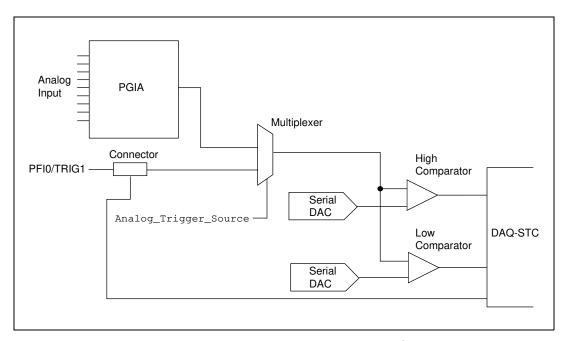

## **Analog Triggering**

The AT-MIO-16E-1, AT-MIO-16E-2, AT-MIO-64E-3, AT-MIO-16XE-10, and AT-AI-16XE-10 have an analog trigger in addition to the digital triggers. To use analog triggering to start an acquisition sequence, select either the PFI0/Trig1 input on the I/O connector or one of the analog input pins. An analog input pin allows you to apply gain to the external signal for more flexible triggering conditions. An INT/EXTTRIG bit in the Misc. Command Register selects the source. PFI0/Trig1 pin has an input voltage range of ±10 V.

An 8-bit serial DAC sets each of the high and low thresholds (except the AT-MIO-16XE-10 and AT-AI-16XE-10). The AT-MIO-16XE-10 and AT-AI-16XE-10 use a 12-bit serial DAC that sets each of the high and low thresholds. These thresholds are within  $\pm$  full scale. The selected input is compared against each of these thresholds by a comparator. The outputs of the comparators are connected to the DAQ-STC analog trigger inputs 0 and 1. Within the DAQ-STC, these signals can be routed to any of the internal timing signals.

You can trigger on either a positive or negative slope or on absolute values.

Refer to the *DAQ-STC Technical Reference Manual* and the *NI-DAQ Function Reference Manual* for more information on analog triggering. For a detailed description of these modes, and timing diagrams, and for a description of other modes not discussed here, refer to the *DAQ-STC Technical Reference Manual*.

# **Analog Output and Timing Circuitry**

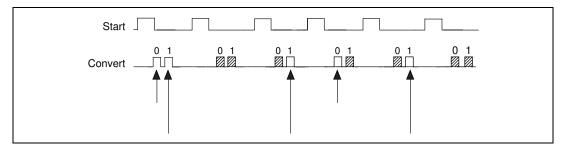

The AT E Series boards have two analog output channels and a timing core within the DAQ-STC that is dedicated to analog output operation. Figure 2-17 shows a general block diagram for the analog output circuitry.

Figure 2-17. Analog Output Circuitry Block Diagram

## **Analog Output Circuitry**

The general model for analog output on the AT E Series boards includes two channels of double-buffered analog output with programmable polarity, reference source, and reglitching circuit, as well as a FIFO to buffer the data. However, not all of the AT E Series boards contain every one of these features. The AT-AI-16XE-10 does not have analog output.

Each analog output channel contains a 12-bit DAC, an amplification stage, and an onboard voltage reference, except for the and AT-MIO-16XE-10, which has a 16-bit DAC. The output voltage will be proportional to the voltage reference (Vref) multiplied by the digital code loaded into the DAC. Note that the output will be set to 0 V on power up. The polarity, reference source, and reglitching circuit are all configured in the AO Configuration Register.

The voltage reference source for each DAC is selectable from the onboard reference or a voltage supplied at the EXTREF pin on the I/O connector, except for the AT-MIO-16XE-50 and AT-MIO-16XE-10, which only supports the onboard reference. The onboard reference is fixed at +10 V. The external reference can be either a DC or an AC signal. If you apply an AC reference, the analog output channel acts as a signal attenuator and the AC signal appears at the output attenuated by the digital code. For unipolar output the voltage is simply attenuated. Four quadrant multiplication occurs in bipolar output, where the signal will not only be attenuated but also inverted for negative digital codes.

The DAC output can be configured to produce either a unipolar or bipolar output range, except for the AT-MIO-16XE-50, which supports only bipolar output. A unipolar output has an output range of 0 to +Vref –1 LSB V. A bipolar output has an output voltage range of -Vref to (+Vref –1 LSB V). For unipolar output, the data written to the DAC is interpreted in straight binary format. For bipolar output, the data is interpreted as two's complement format. One LSB is the voltage increment corresponding to an LSB change in the digital code word. For unipolar output, 1 LSB = (Vref)/4,096. For bipolar output, 1 LSB = (Vref)/2,048. For 16-bit DAC, 1 LSB = (Vref)/8,192 in unipolar mode and 1 LSB = (Vref)/4,096 in bipolar mode.

Using the 12-bit DAC and onboard 10 V reference will produce an output voltage range of 0 to 9.9976 V in steps of 2.44 mV for unipolar output and an output voltage range of -10 V to +9.9951 V in steps of 4.88 mV for bipolar operation. Using 16-bit DAC and onboard 10 V reference will produce an output range of 0 to 9.9986 V in steps of 1.22 mV for unipolar output and an output voltage range of -10 to +9.9976 V in steps of 2.44 mV for bipolar operation.

In normal operation, a DAC output will glitch whenever it is updated with a new value. The glitch energy differs from code to code and appears as distortion in the frequency spectrum. Each analog output of the AT-MIO-16E-1, AT-MIO-16E-2, and AT-MIO-64E-3 contains a reglitch circuit that generates uniform glitch energy at every code rather than large glitches at the major code transitions. This uniform glitch energy appears as a multiple of the update rate in the frequency spectrum. Notice that this reglitch circuit does not eliminate the glitches; it only makes them more uniform in size.

The AT-MIO-16E-1, AT-MIO-16E-2, AT-MIO-64E-3, and AT-MIO-16XE-10 include 2 kword-deep FIFOs to buffer the analog output data. This buffering will increase the maximum rate that the analog output

can sustain for waveform generation. It can also be used to store a complete waveform which can be output repetitively without any further data transfer to the FIFO.

## **Analog Output Timing Circuitry**

This section describes the different methods of setting the analog output voltage, including single-point updating and waveform generation. The DAQ-STC and DAQ-PnP provide the timing signals necessary to write to the DACs and update them.

The DACs are double buffered and can be individually configured for immediate update or timed update mode. In immediate update mode, the double buffering of the DAC is disabled and the value written to the DAC will appear immediately on the output after the write completes. In the timed update mode, the double buffering is enabled. When double buffering is enabled, writing the digital value loads that value into the buffer stage of the DAC. When an update signal is received, the analog output of the DAC changes.

## **Single-Point Output**

The data values can be written directly to the DACs under software control without the use of the timing engine provided in the DAQ-STC. This is typically useful for setting the analog outputs to DC levels, where precise timing of the output change is not important. Writing directly to the DACs is accomplished by writing the desired value to the DAC<0..1> Direct Data Register. This action will store the value in the first buffer of the DAC. If the DAQ-STC is programmed for immediate updating mode, the value will also be applied to the analog output. If the DAQ-STC is programmed for timed updating mode, the appropriate update signal, LDAC0\* or LDAC1\*, must be asserted by writing to the appropriate DAQ-STC register.

#### **Waveform Generation**

The timing engine in the DAQ-STC can be used for waveform generation, where the update signals connected to the DACs can be generated at precise intervals. In this model, the DAQ-STC will generate the update signals and then transfer the data values for the next update to the first buffer of the DACs.

The update interval counter (UI) is 24 bits wide and generates the update pulses. These update pulses can be routed to the DACs. The update counter (UC) is 24 bits wide and counts the number of updates. The value loaded into this counter defines a buffer. The buffer counter (BC) determines how

many times a buffer should be repeated. These counters define an analog output sequence.

The DAQ-STC will transfer the data values for the next update after each update pulse. This data transfer will be from the analog output FIFO. Some of the boards have large 2 kword FIFOs; others are zero-deep virtual FIFOs. The large FIFOs are true FIFOs, where data can be written to the FIFOs so long as they are not full and can be read from when they are not empty. In this case, the DAQ-STC will transfer the data from the FIFO to the DACs when the FIFO is not empty. If the FIFO is empty, the DAQ-STC will delay the transfer until more data is written into the FIFO.

The zero-deep virtual FIFOs are not true FIFOs, but they do provide a software compatible method for waveform generation. When the DAQ-STC generates an update signal and is ready to transfer data, the DAQ-PnP will clear the FIFO full flag. This FIFO full flag can be used by interrupts or DMA to transfer data to the virtual FIFO. The virtual FIFO will not actually buffer the data, instead it will transfer it directly to the first buffer of the destination DAC. After the data has been transferred, the DAQ-PnP will set the FIFO full flag, indicating that no more data is required. Note that the half-full and empty flags do not provide useful information for data transfer and should not be used.

The large FIFOs can also be used to generate repetitive waveforms at very high speeds and without using any bus bandwidth. The FIFOs can be loaded with the desired waveform and the DAQ-STC can be programmed to retransmit the same FIFO data to the DACs over and over. When the FIFO is empty, the retransmit signal is asserted, which restores that FIFO data to its original state.

When both DACs are used in waveform generation, the data in the FIFO is interleaved; in other words, every alternate sample belongs to one DAC.

# Digital I/O Circuitry

The AT E Series boards have eight digital I/O lines. Each of the eight digital lines can be individually programmed to be input or output, if used in parallel. For serial data transfer, DIO4 is used as the serial data in pin, and DIO0 is used as the serial data out pin.

You can use handshaking with the EXTSTROBE\* pin to do either parallel or serial data transfer. Refer to the *DAQ-STC Technical Reference Manual* for more details on the DIO features.

The external strobe signal EXTSTROBE\* is a general-purpose strobe signal. Software can set the output of the EXTSTROBE\* pin to either a high or low state. EXTSTROBE\* is not necessarily part of the digital I/O circuitry but is included here because you can use it to latch digital output from the AT E Series into an external device.

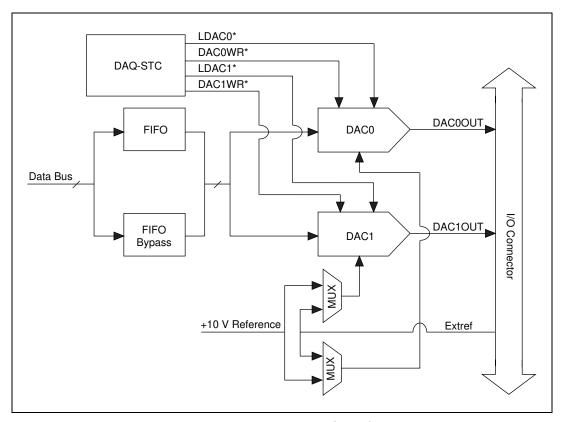

## Timing I/O Circuitry

The DAQ-STC has two 24-bit general purpose counter/timers. The counters are numbered 0 and 1 and are diagrammed as shown in Figure 2-18.

Figure 2-18. DAQ-STC Counter Diagram

The counter counts the transitions, or edges, on the SOURCE line when the GATE is enabled and generates timing signals at its OUT output pin. The UPDOWN pin determines the direction of counting. Active polarities of these pins are software selectable in the DAQ-STC. Notice that on the AT E Series only the SOURCE, GATE, and OUT pins are brought out to the I/O connector. The UPDOWN pin for counter 0 is internally connected to DIO6 and to DIO7 for counter 1. To drive the UPDOWN pin from the connector, you must tri-state the corresponding DIO line.

The SOURCE of these counters can be selected to be one of the 10 PFI lines or the seven RTSI lines, or the internal 20 MHz or 100 kHz timebases, or the TC of the other counter. With the last option, the two counters can be concatenated. Similarly, the GATE can also be selected from a variety of different sources. The sources for both of these signals are described in the DAQ-STC Technical Reference Manual.

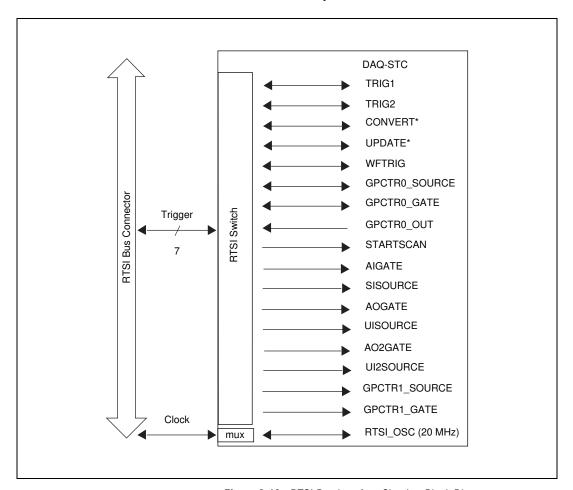

## **RTSI Bus Interface Circuitry**

The AT E Series is interfaced to the National Instruments RTSI bus. The RTSI bus has seven trigger lines and a system clock line. You can wire all National Instruments AT E Series boards with RTSI bus connectors inside the PC AT and share these signals. Figure 2-19 shows a block diagram of the RTSI bus interface circuitry.

Figure 2-19. RTSI Bus Interface Circuitry Block Diagram

The RTSI functionality is provided in the DAQ-STC chip. This RTSI Trigger Module consists of seven 12-to-1 multiplexers that drive seven RTSI Trigger bus signals and four 8-to-1 multiplexers that drive the four RTSI Board signals.

Any of the seven RTSI Trigger bus signals can be driven by eight internally generated timing signals and the four RTSI Board signals. Similarly, the four RTSI Board signals can be driven by any of the RTSI Trigger bus signals. Of the four RTSI board signals, only one is used. By programming certain bits in the DAQ-STC, you can drive the CONVERT pulse onto RTSI\_BRD0 and then onto any of the TRIGGER lines.

# **Register Map and Descriptions**

This chapter describes in detail the address and function of each of the AT E Series control and status registers.

If you plan to use a programming software package such as NI-DAQ for DOS/Windows or Lab Windows with your AT E Series board, you need not read this chapter. However, you will gain added insight into your AT E Series board by reading this chapter.

## Register Map

Table 3-1 shows the register map for the AT E Series boards and gives the register name, the register offset address, the type of the register (read-only, write-only, or read-and-write), and the size of the register in bits. Obtain the actual register address by adding the appropriate register offset to the I/O base address of the AT E Series board.

Registers are grouped in the table by function. Each register group is introduced in the order shown in Table 3-1, then described in detail, including a bit-by-bit description.

The DAQ-STC has 180 different registers. The more frequently used registers have been given lower offset addresses and are shown in Table 3-1 as the DAQ-STC Register Group. The advantage of having lower offset addresses is that they can be accessed directly. You can access remaining registers in the DAQ-STC in the windowed mode. In this mode, the address of the register is first written to the Window Address Register. The data to be written is then written to the Window Data Register. Using windowed mode has the advantage of reducing the address space of the board from 180 to 32 bytes. However, this reduced address space is at the cost of two write operations to write data to or two read operations to read data from a register.

Table 3-1. AT E Series Register Map

|                              | Offset Address |         |            |        |

|------------------------------|----------------|---------|------------|--------|

| Register Name                | Hex            | Decimal | Туре       | Size   |

| Misc Register Group          |                |         |            |        |

| Serial Command               | 0D             | 13      | Write-only | 8-bit  |

| Misc Command                 | 0F             | 15      | Write-only | 8-bit  |

| Status                       | 01             | 1       | Read-only  | 8-bit  |

| Analog Input Register Group  |                |         |            |        |

| ADC FIFO Data Register       | 1C             | 28      | Read-only  | 16-bit |

| Configuration Memory Low     | 10             | 16      | Write-only | 16-bit |

| Configuration Memory High    | 12             | 18      | Write-only | 16-bit |

| Analog Output Register Group |                |         |            |        |

| AO Configuration             | 16             | 22      | Write-only | 16-bit |

| DAC FIFO Data                | 1E             | 30      | Write-only | 16-bit |

| DAC0 Direct Data             | 18             | 24      | Write-only | 16-bit |

| DAC1 Direct Data             | 1A             | 26      | Write-only | 16-bit |

| DMA Control Register Group   |                |         |            |        |

| Strobes                      | 01             | 1       | Write-only | 16-bit |

| Channel A Mode               | 03             | 3       | Write-only | 16-bit |

| Channel B Mode               | 05             | 5       | Write-only | 16-bit |

| Channel C Mode               | 07             | 7       | Write-only | 16-bit |

| AI AO Select                 | 09             | 9       | Write-only | 16-bit |

| G0 G1 Select                 | 0B             | 11      | Write-only | 16-bit |

Table 3-1. AT E Series Register Map (Continued)

|                         | Offset A | Address |                |        |

|-------------------------|----------|---------|----------------|--------|

| Register Name           | Hex      | Decimal | Туре           | Size   |

| DIO Register Group      |          |         |                |        |

| Port A                  | 19       | 25      | Read-and-write | 8-bit  |

| Port B                  | 1B       | 27      | Read-and-write | 8-bit  |

| Port C                  | 1D       | 29      | Read-and-write | 8-bit  |

| Configuration           | 1F       | 31      | Write-only     | 8-bit  |

| DAQ-STC Register Group  |          |         | Read-and-write | 16-bit |

| Window Address          | 0        | 0       | Read-and-write | 16-bit |

| Window Data             | 2        | 2       | Write          | 16-bit |

| Interrupt A Acknowledge | 4        | 4       | Write          | 16-bit |

| Interrupt B Acknowledge | 6        | 6       | Write          | 16-bit |

| AI Command 2            | 8        | 8       | Write          | 16-bit |

| AO Command 2            | A        | 10      | Write          | 16-bit |

| G0 Command              | С        | 12      | Write          | 16-bit |

| G1 Command              | Е        | 14      | Write          | 16-bit |

| AI Status 1             | 4        | 4       | Read           | 16-bit |

| AO Status 1             | 6        | 6       | Read           | 16-bit |

| G Status                | 8        | 8       | Read           | 16-bit |

| AI Status 2             | A        | 10      | Read           | 16-bit |

| AO Status 2             | C        | 12      | Read           | 16-bit |

| DIO Parallel Input      | Е        | 14      | Read           | 16-bit |

Table 3-2.

AT E Series Windowed Register Map

|                            | Word Offset |         |            |        |

|----------------------------|-------------|---------|------------|--------|

| Register Name              | Hex         | Decimal | Туре       | Size   |

| FIFO Strobe Register Group |             |         |            |        |

| Configuration Memory Clear | 52          | 82      | Write-only | 16-bit |

| ADC FIFO Clear             | 53          | 83      | Write-only | 16-bit |

| DAC FIFO Clear             | 54          | 84      | Write-only | 16-bit |

#### **Register Sizes**

Two different transfer sizes for read-and-write operations are available on the PC—byte (8-bit) and word (16-bit). Table 3-1 shows the size of each AT E Series register. For example, reading the ADC FIFO Data Register requires a 16-bit (word) read operation at the selected address, whereas writing to the Misc Command Register requires an 8-bit (byte) write operation at the selected address. For proper board operation you must adhere to these register size accesses. Avoid performing a byte access on a word location or performing a word access on a byte location; these are invalid operations. Pay particular attention to the register sizes; they are very important.

## **Register Descriptions**

This section discusses each of the AT E Series registers in the order shown in Table 3-1. Each register group is introduced, followed by a detailed bit description. The individual register description gives the address, type, word size, and bit map of the register, followed by a description of each bit.

The register bit map shows a diagram of the register with the MSB shown on the left (bit 15 for a 16-bit register, bit 7 for an 8-bit register), and the LSB shown on the right (bit 0). A square represents each bit and contains the bit name. An asterisk (\*) after the bit name indicates that the bit is inverted (negative logic).

In many of the registers, several bits are labeled Reserved. When a register is read, these bits may appear set or cleared but should be ignored because they have no significance. When a register is written, these bits should be set to zero.

### Misc Register Group

The three registers making up the Misc Register Group include two command registers that control the serial DACs, EEPROM, and analog trigger source, and one status register that includes EEPROM and DMA information.

Bit descriptions of the three registers making up the Misc Register Group are given on the following pages.

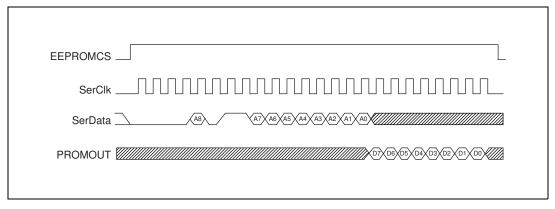

## **Serial Command Register**

The Serial Command Register contains six bits that control AT E Series serial EEPROM and DACs. The contents of this register are cleared upon power up and after a reset condition.

**Address:** Base address + 0D (hex)

**Type:** Write-only

Name

Word Size: 8-bit

Bit Map:

Bit

| 7        | 6        | 5         | 4         | 3         | 2        | 1       | 0      |

|----------|----------|-----------|-----------|-----------|----------|---------|--------|

| Reserved | Reserved | SerDacLd2 | SerDacLd1 | SerDacLd0 | EEPromCS | SerData | SerClk |

Description

| DIL | Manie     | Description                                                                                                                                                                                                     |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–4 | Reserved  | Reserved—Always write 0 to these bits.                                                                                                                                                                          |

| 5   | SerDacLd2 | Serial DAC Load2—This bit is used to load the third set of serial DACs with the serial data previously shifted into the DACs ( <i>AT-MIO-16XE-10 and AT-AI-16XE-10 only</i> ).                                  |

| 4   | SerDacLd1 | Serial DAC Load1—This bit is used to load the second set of serial DACs with the serial data previously shifted into the DACs ( <i>AT-MIO-16XE-50</i> , <i>AT-MIO-16XE-10</i> , and <i>AT-AI-16XE-10</i> only). |

| 3   | SerDacLd0 | Serial DAC Load0—This bit is used to load the first set of serial DACs with the serial data previously shifted into the DACs.                                                                                   |

| 2   | EEPromCS  | EEPROM Chip Select—This bit controls the chip select of the onboard EEPROM used to store calibration constants. When EEPromCS is set, the chip select signal to the EEPROM is enabled.                          |

SerData

Serial Data—This bit is the data for the onboard serial devices—the calibration EEPROM and the serial DACs.

This bit should be set to the desired value prior to the active write to the SerClk bit.

SerClk

Serial Clock—This bit is the clock input to the onboard serial device. In order to write to these devices, this bit should be set first to 0 and then to 1. The data in the SerData bit will be written to the devices on the low-to-high transition of the serial clock.

#### **Misc Command Register**

The Misc Command Register contains one bit that controls the AT E Series analog trigger source. The contents of this register are cleared upon power up and after a reset condition.

**Address:** Base address + 0F (hex)

**Type:** Write-only

Word Size: 8-bit

| 7            | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|--------------|----------|----------|----------|----------|----------|----------|----------|

| Int/Ext Trig | Reserved |

| Bit | Name         | Description                                                                                                                                                                                                                                                    |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Int/Ext Trig | Internal/External Analog Trigger—This bit controls the analog trigger source. If this bit is set, the output of the PGIA is selected as the trigger source. If this bit is cleared, the TRIG1 signal from the I/O connector is selected as the trigger source. |

| 6-0 | Reserved     | Reserved—Always write 0 to these bits.                                                                                                                                                                                                                         |

## **Status Register**

The Status Register is used to indicate the status of the DMATCs and the calibration EEPROM output.

Chapter 3

**Address:** Base address + 01 (hex)

**Type:** Read-only

Word Size: 8-bit

| 7        | 6        | 5        | 4        | 3      | 2      | 1      | 0       |   |

|----------|----------|----------|----------|--------|--------|--------|---------|---|

| Reserved | Reserved | Reserved | Reserved | DMATCC | DMATCB | DMATCA | PROMOUT | ı |

| Bit | Name     | Description                                                                                                                                                                                                                        |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–4 | Reserved | Reserved—Always write 0 to these bits.                                                                                                                                                                                             |

| 3   | DMATCC   | DMA Terminal Count C—This bit indicates the status of the DMA process on the selected DMA Channel C. When all transfers have been completed, DMATCC will be set. This bit is cleared by the DmaTcCClr bit in the Strobes Register. |

| 2   | DMATCB   | DMA Terminal Count B—This bit indicates the status of the DMA process on the selected DMA Channel B. When all transfers have been completed, DMATCB will be set. This bit is cleared by the DmaTcBClr bit in the Strobes Register. |

| 1   | DMATCA   | DMA Terminal Count A—This bit indicates the status of the DMA process on the selected DMA Channel A. When all transfers have been completed, DMATCA will be set. This bit is cleared by the DmaTcAClr bit in the Strobes Register. |

| 0   | PROMOUT  | EEPROM Output Data—This bit reflects the serial output data of the serial EEPROM.                                                                                                                                                  |

## **Analog Input Register Group**

The three registers making up the Analog Input Register Group control the analog input circuitry and can be used to read the ADC FIFO contents. Reading the ADC FIFO Data Register location transfers data from the AT E Series ADC data FIFO to the PC. Writing to the Configuration Memory Low and Configuration Memory High Register locations sets up channel configuration information for the analog input section. This information is necessary for single conversions as well as for single- and multiple-channel data acquisition sequences.

#### **ADC FIFO Data Register**

The ADC FIFO Data Register returns the oldest ADC conversion value stored in the ADC FIFO. Reading the ADC FIFO removes that value and leaves space for another ADC conversion value to be stored. Values are shifted into the ADC FIFO whenever an ADC conversion is complete unless the GHOST bit is set in that entry of the Configuration Memory.

The ADC FIFO is emptied when all values it contains are read. The empty, half-full, and full flags from the ADC data FIFO are available in a status register in the DAQ-STC. These flags indicate when the FIFO is empty, half-full, or full, respectively. Whenever the FIFO is not empty, the stored data can be read from the ADC FIFO Data register.

The values returned by reading the ADC Data Register are available in two different binary formats: straight binary, which generates only positive numbers, or two's complement binary, which generates both positive and negative numbers. The binary format used is determined by the mode in which the ADC is configured. Following is the bit pattern returned for either format:

**Address:** Base address + 1C (hex)

**Type:** Read-only

Word Size: 16-bit

| 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  |